# SH-4

Hardware Manual *Preliminary*

# **HITACHI**

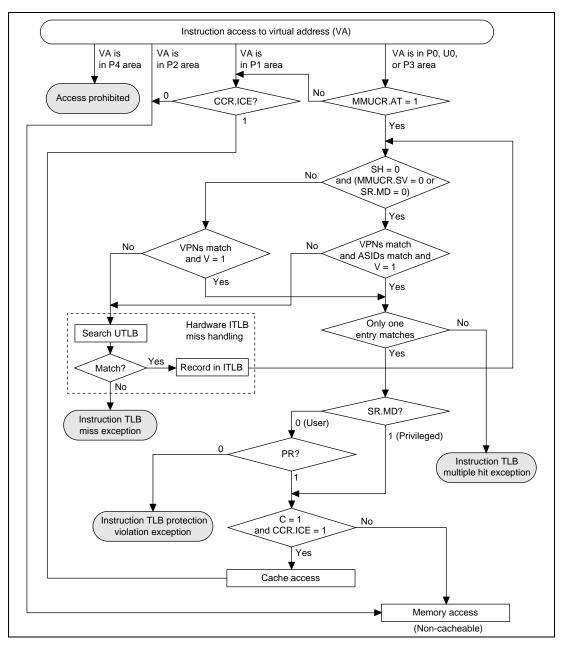

Version 1.1 7/31/98 Hitachi, Ltd.

# Notice

When using this document, keep the following in mind:

- 1. This document may, wholly or partially, be subject to change without notice.

- 2. All rights are reserved: No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without Hitachi's permission.

- 3. Hitachi will not be held responsible for any damage to the user that may result from accidents or any other reasons during operation of the user's unit according to this document.

- 4. Circuitry and other examples described herein are meant merely to indicate the characteristics and performance of Hitachi's semiconductor products. Hitachi assumes no responsibility for any intellectual property claims or other problems that may result from applications based on the examples described herein.

- 5. No license is granted by implication or otherwise under any patents or other rights of any third party or Hitachi, Ltd.

- 6. MEDICAL APPLICATIONS: Hitachi's products are not authorized for use in MEDICAL APPLICATIONS without the written consent of the appropriate officer of Hitachi's sales company. Such use includes, but is not limited to, use in life support systems. Buyers of Hitachi's products are requested to notify the relevant Hitachi sales offices when planning to use the products in MEDICAL APPLICATIONS.

# Contents

| Contents                                                          | i  |

|-------------------------------------------------------------------|----|

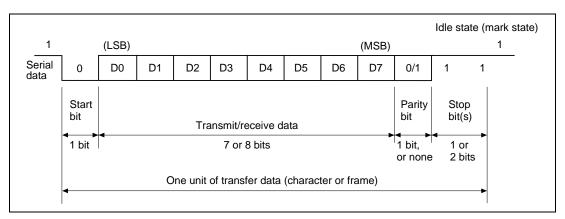

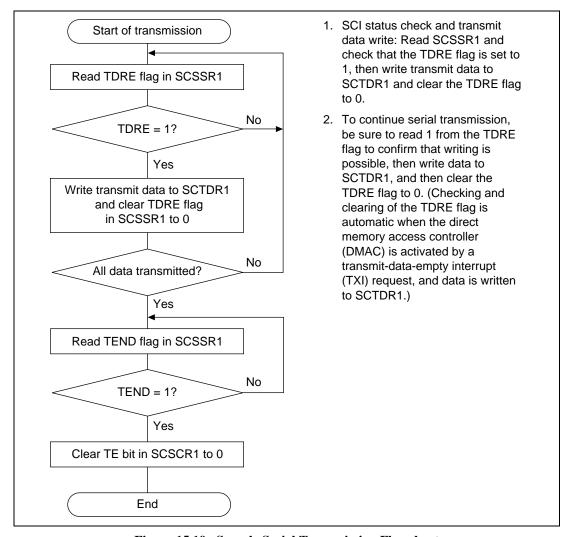

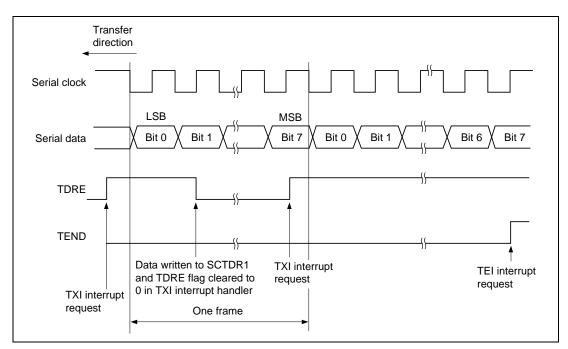

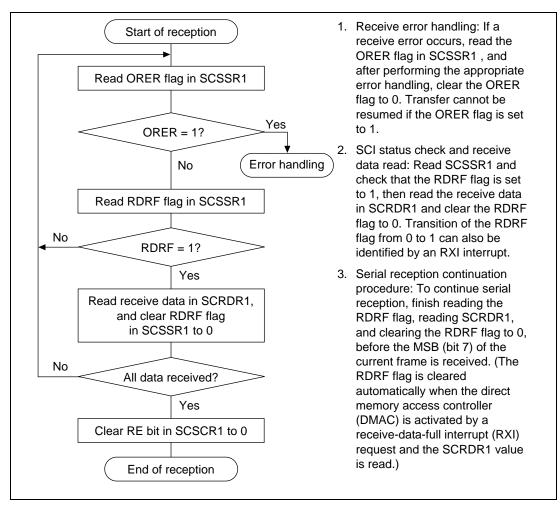

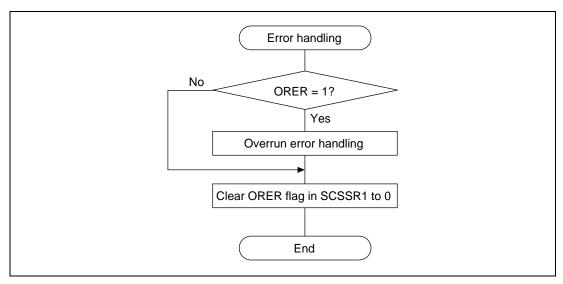

| Section 1 Overview                                                | 13 |

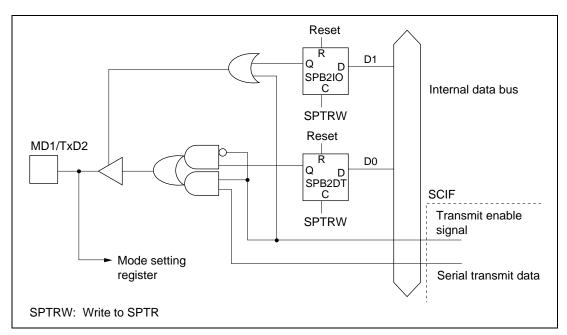

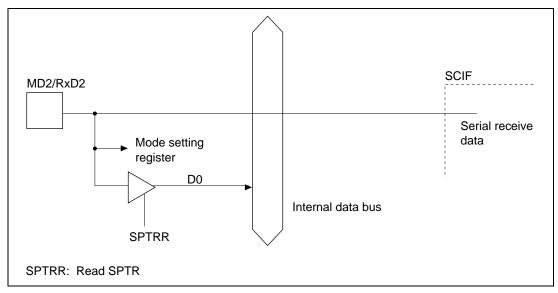

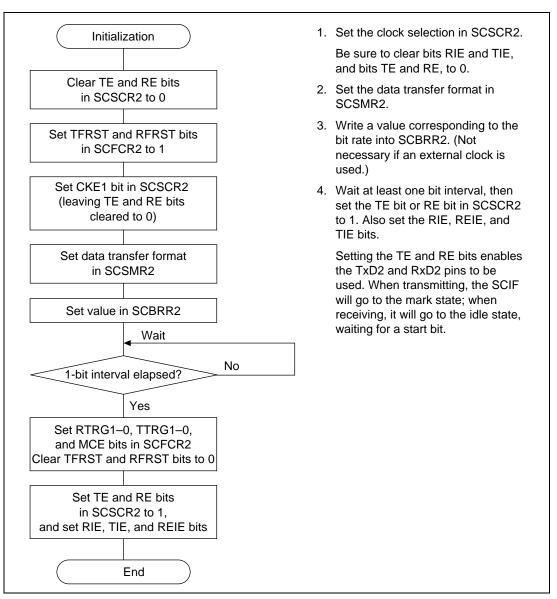

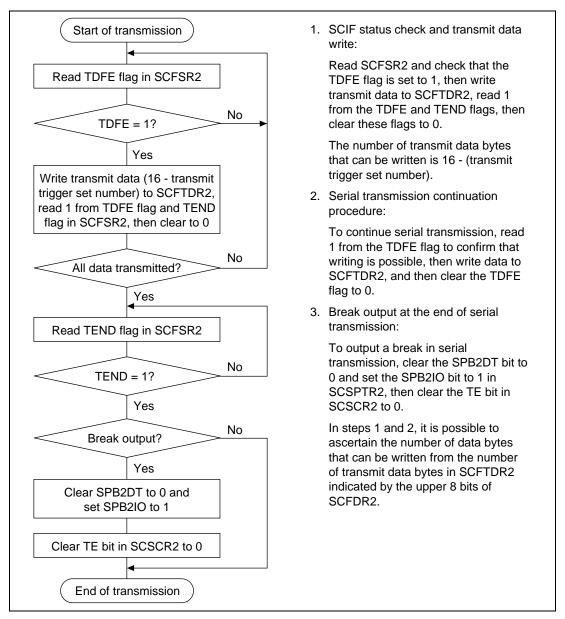

| 1.1 SH7750 Features                                               | 13 |

| 1.2 Block Diagram                                                 | 20 |

| Section 2 Programming Model                                       | 21 |

| 2.1 Data Formats                                                  |    |

| 2.2 Register Configuration                                        |    |

| 2.2.1 Privileged Mode and Banks                                   |    |

| 2.2.2 General Registers                                           |    |

| 2.2.3 Floating-Point Registers                                    |    |

| 2.2.4 Control Registers                                           |    |

| 2.2.5 System Registers                                            |    |

| 2.3 Memory-Mapped Registers                                       |    |

| 2.4 Data Format in Registers.                                     |    |

| 2.5 Data Formats in Memory                                        |    |

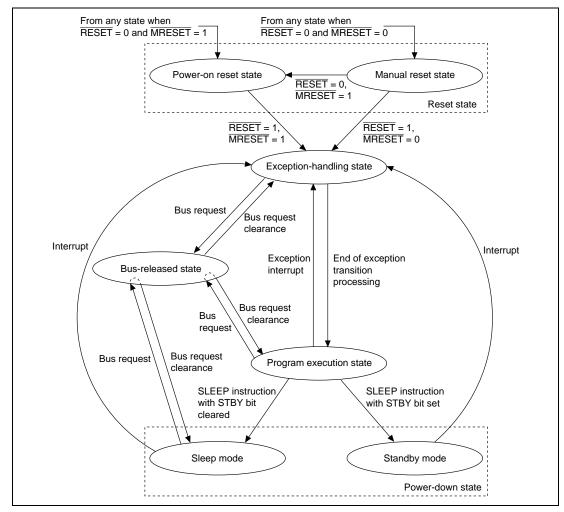

| 2.6 Processor States                                              |    |

| 2.7 Processor Modes                                               |    |

| 3.1 Overview                                                      |    |

| 3.1.1 Features                                                    | 37 |

| 3.1.2 Role of the MMU                                             | 37 |

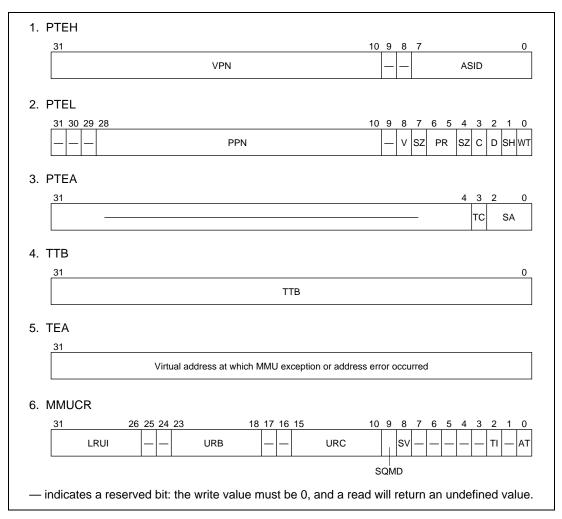

| 3.1.3 Register Configuration                                      | 40 |

| 3.1.4 Caution                                                     | 40 |

| 3.2 Register Descriptions                                         | 41 |

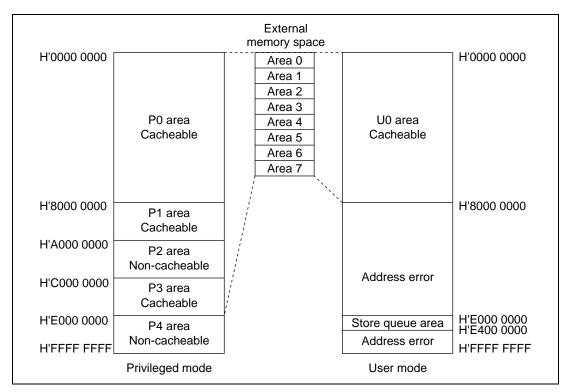

| 3.3 Memory Space                                                  | 44 |

| 3.3.1 Physical Memory Space                                       | 44 |

| 3.3.2 External Memory Space                                       | 47 |

| 3.3.3 Virtual Memory Space                                        | 48 |

| 3.3.4 On-Chip RAM Space                                           | 49 |

| 3.3.5 Address Translation                                         | 49 |

| 3.3.6 Single Virtual Memory Mode and Multiple Virtual Memory Mode |    |

| 3.3.7 Address Space Identifier (ASID)                             |    |

| 3.4 TLB Functions                                                 |    |

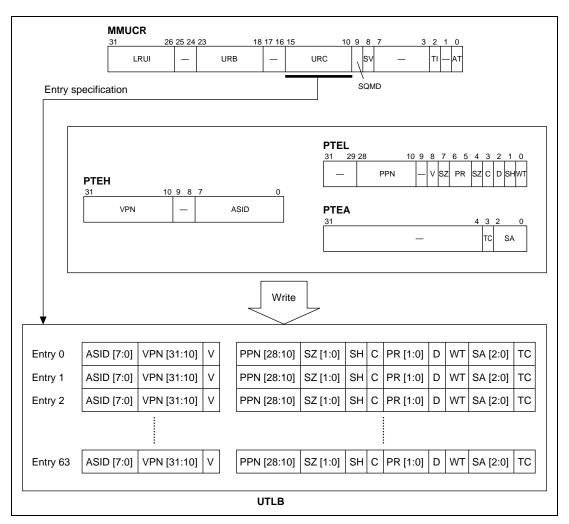

| 3.4.1 Unified TLB (UTLB) Configuration                            | 51 |

| 3.4.2 Instruction TLB (ITLB) Configuration                        |    |

| 3.4.3 Address Translation Method                                  |    |

| 3.5 MMU Functions                                                 |    |

| 3.5.1 MMU Hardware Management                                     | 58 |

Rev. 2.0, 02/99, page i of xii

| 3.5.2 MMU Software Management                        | 58 |

|------------------------------------------------------|----|

| 3.5.3 MMU Instruction (LDTLB)                        | 58 |

| 3.5.4 Hardware ITLB Miss Handling                    | 59 |

| 3.5.5 Avoiding Synonym Problems                      | 60 |

| 3.6 MMU Exceptions                                   | 61 |

| 3.6.1 Instruction TLB Multiple Hit Exception         | 61 |

| 3.6.2 Instruction TLB Miss Exception                 | 62 |

| 3.6.3 Instruction TLB Protection Violation Exception | 63 |

| 3.6.4 Data TLB Multiple Hit Exception                | 64 |

| 3.6.5 Data TLB Miss Exception                        | 64 |

| 3.6.6 Data TLB Protection Violation Exception        | 65 |

| 3.6.7 Initial Page Write Exception                   | 66 |

| 3.7 Memory-Mapped TLB Configuration                  | 67 |

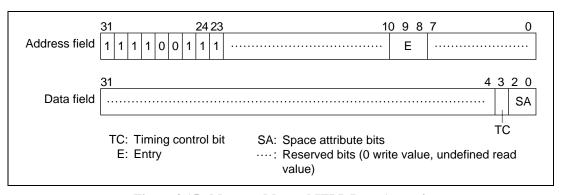

| 3.7.1 ITLB Address Array                             | 68 |

| 3.7.2 ITLB Data Array 1                              | 69 |

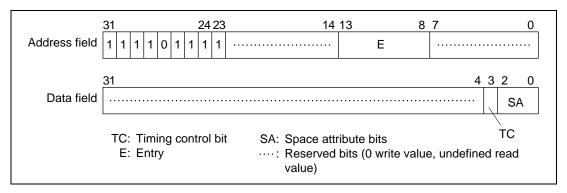

| 3.7.3 ITLB Data Array 2                              | 70 |

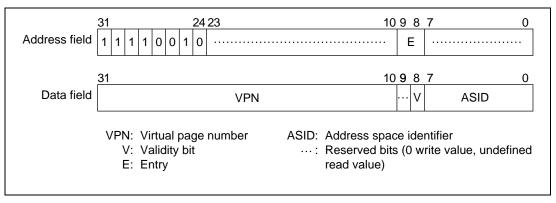

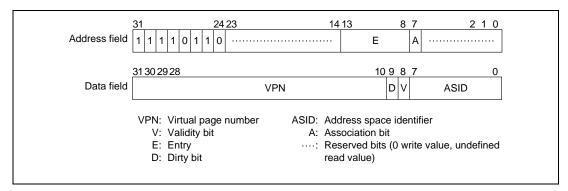

| 3.7.4 UTLB Address Array                             | 71 |

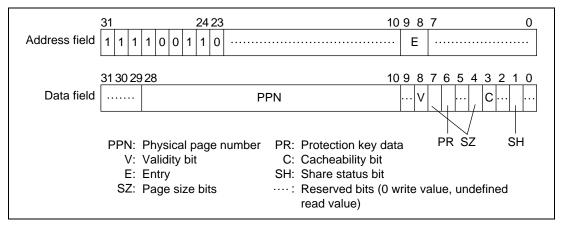

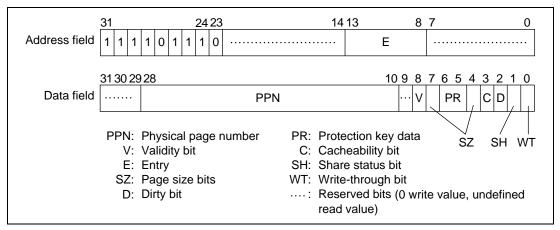

| 3.7.5 UTLB Data Array 1                              | 72 |

| 3.7.6 UTLB Data Array 2                              | 73 |

| 4.1 Overview                                         | 75 |

| 4.1.1 Features                                       | 75 |

| 4.1.2 Register Configuration                         | 76 |

| 4.2 Register Descriptions                            | 76 |

| 4.3 Operand Cache (OC)                               | 79 |

| 4.3.1 Configuration                                  | 79 |

| 4.3.2 Read Operation                                 | 80 |

| 4.3.3 Write Operation                                | 81 |

| 4.3.4 Write-Back Buffer                              | 83 |

| 4.3.5 Write-Through Buffer                           | 83 |

| 4.3.6 RAM Mode                                       | 83 |

| 4.3.7 OC Index Mode                                  | 84 |

| 4.3.8 Coherency between Cache and External Memory    | 85 |

| 4.3.9 Prefetch Operation                             | 85 |

| 4.4 Instruction Cache (IC)                           | 86 |

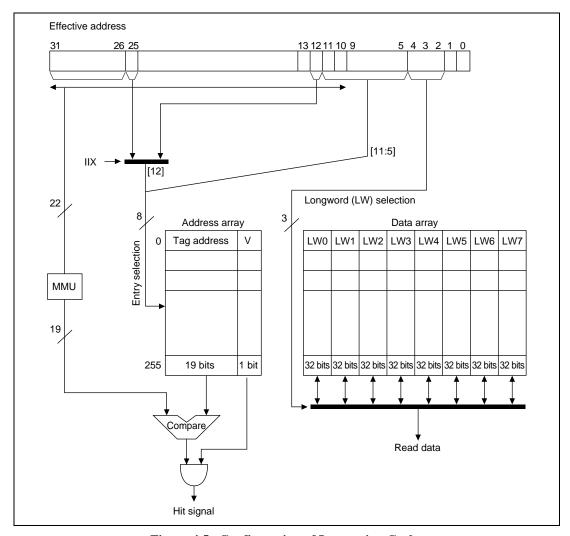

| 4.4.1 Configuration                                  | 86 |

| 4.4.2 Read Operation                                 | 87 |

| 4.4.3 IC Index Mode                                  | 88 |

| 4.5 Memory-Mapped Cache Configuration                | 88 |

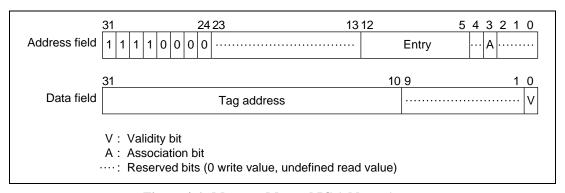

| 4.5.1 IC Address Array                               | 88 |

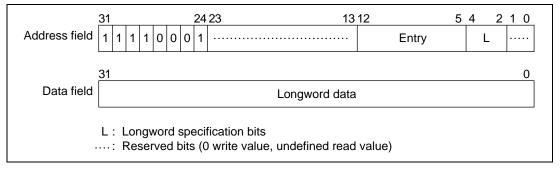

| 4.5.2 IC Data Array                                  | 90 |

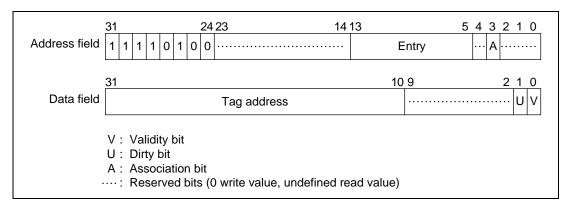

| 4.5.3 OC Address Array                               | 91 |

| 4.5.4 OC Data Array                                  | 92 |

| 4.6 Store Queues                                     | 93 |

|                                                      |    |

Rev. 2.0, 02/99, page ii of xii

| 4.6.1 SQ Configuration                               | 93    |

|------------------------------------------------------|-------|

| 4.6.2 SQ Writes                                      | . 94  |

| 4.6.3 Transfer to External Memory                    | .94   |

| 4.6.4 SQ Protection                                  | . 95  |

| Section 5 Everations                                 | 07    |

| Section 5 Exceptions                                 |       |

| 5.1.1 Features                                       |       |

|                                                      |       |

| 5.1.2 Register Configuration                         |       |

| 5.2 Register Descriptions                            |       |

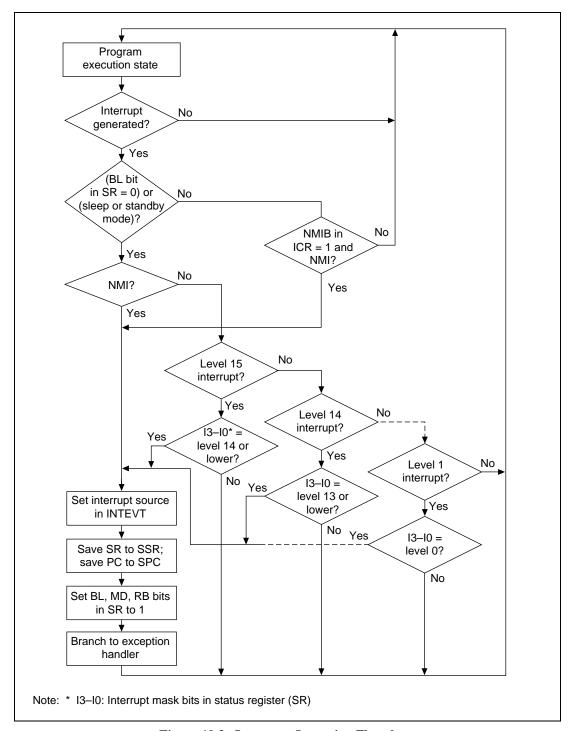

| 5.3 Exception Handling Functions                     |       |

| 5.3.1 Exception Handling Flow                        |       |

| 5.3.2 Exception Handling Vector Addresses            |       |

| 5.4 Exception Types and Priorities                   |       |

| 5.5 Exception Flow                                   |       |

| 5.5.1 Exception Flow                                 |       |

| 5.5.2 Exception Source Acceptance                    |       |

| 5.5.3 Exception Requests and BL Bit                  |       |

| 5.5.4 Return from Exception Handling                 |       |

| 5.6 Description of Exceptions                        |       |

| 5.6.1 Resets                                         |       |

| 5.6.2 General Exceptions                             |       |

| 5.6.3 Interrupts                                     |       |

| 5.6.4 Priority Order with Multiple Exceptions        |       |

| 5.7 Usage Notes                                      |       |

| 5.8 Restrictions                                     | . 131 |

| Section 6 Floating-Point Unit                        | .133  |

| 6.1 Overview                                         | 133   |

| 6.2 Data Formats.                                    | 133   |

| 6.2.1 Floating-Point Format                          | 133   |

| 6.2.2 Non-Numbers (NaN)                              | 135   |

| 6.2.3 Denormalized Numbers                           | 136   |

| 6.3 Registers                                        | 137   |

| 6.3.1 Floating-Point Registers                       | . 137 |

| 6.3.2 Floating-Point Status/Control Register (FPSCR) | 139   |

| 6.3.3 Floating-Point Communication Register (FPUL)   | 140   |

| 6.4 Rounding                                         |       |

| 6.5 Floating-Point Exceptions                        | 141   |

| 6.6 Graphics Support Functions                       | . 143 |

| 6.6.1 Geometric Operation Instructions               | 143   |

| 6.6.2 Pair Single-Precision Data Transfer            | 144   |

| 7.1 Execution Environment                            | 1/15  |

| 7.2 Addressing Modes                               | 147 |

|----------------------------------------------------|-----|

| 7.3 Instruction Set                                | 151 |

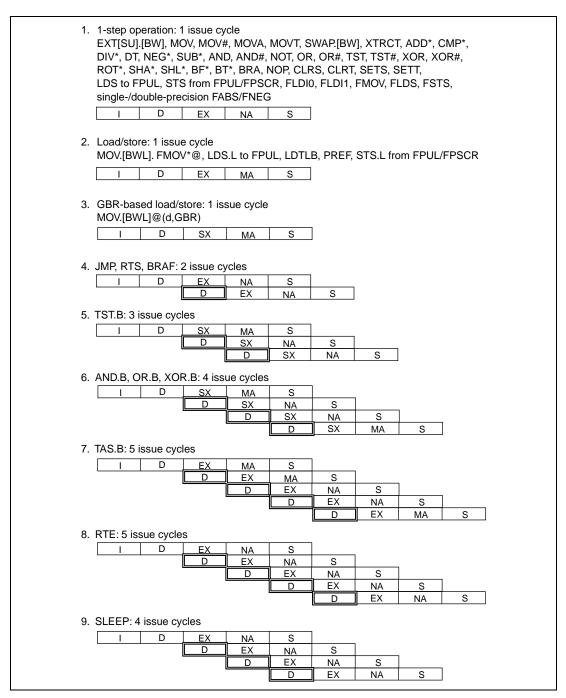

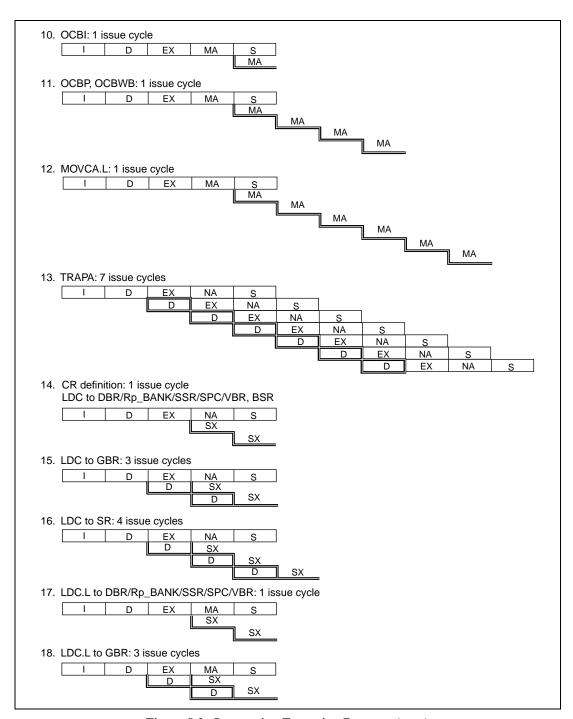

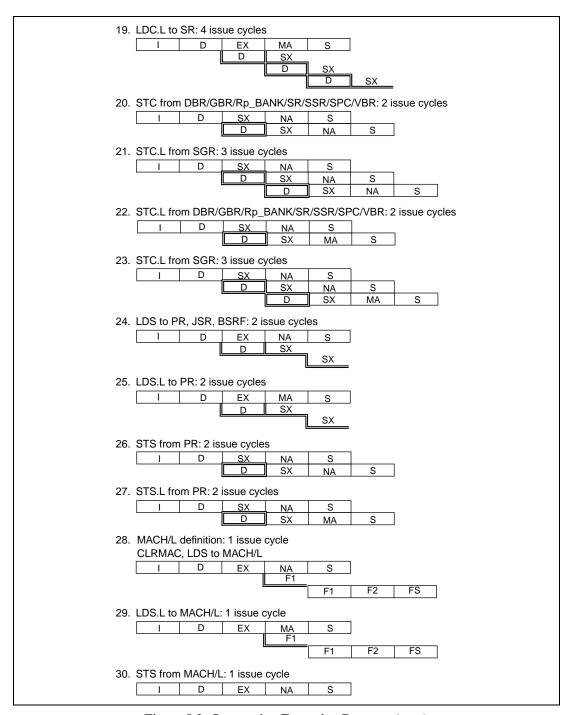

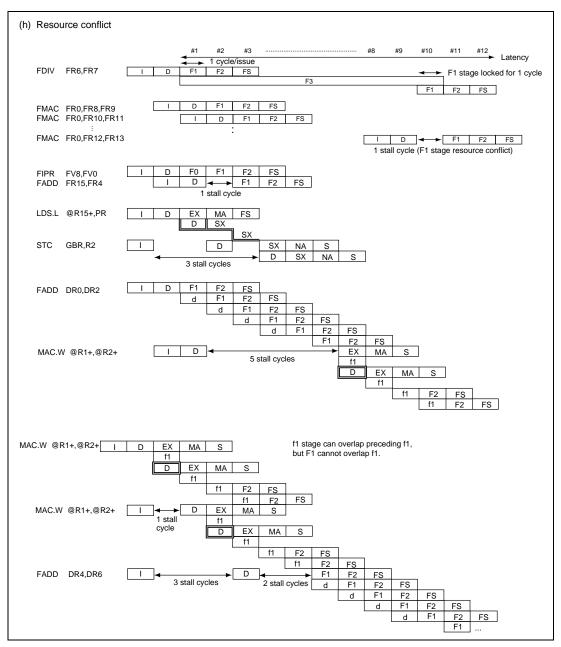

| Section 8 Pipelining                               | 165 |

| 8.1 Pipelines                                      |     |

| 8.2 Parallel-Executability.                        |     |

| 8.3 Execution Cycles and Pipeline Stalling         |     |

| 9.1 Overview                                       |     |

| 9.1.1 Types of Power-Down Modes                    |     |

| 9.1.2 Register Configuration                       |     |

| 9.1.3 Pin Configuration                            |     |

| 9.2 Register Descriptions                          |     |

| 9.2.1 Standby Control Register (STBCR)             |     |

| 9.2.2 Peripheral Module Pin High Impedance Control |     |

| 9.2.3 Peripheral Module Pin Pull-Up Control        | 198 |

| 9.2.4 Standby Control Register 2 (STBCR2)          | 199 |

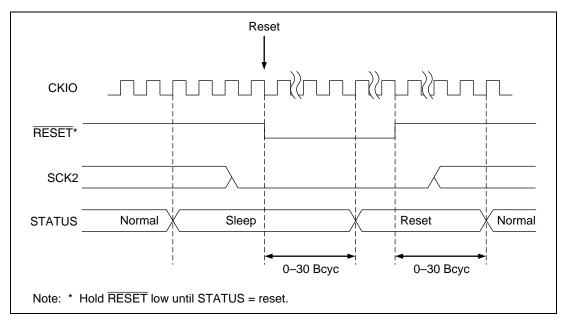

| 9.3 Sleep Mode                                     | 200 |

| 9.3.1 Transition to Sleep Mode                     | 200 |

| 9.3.2 Exit from Sleep Mode                         | 200 |

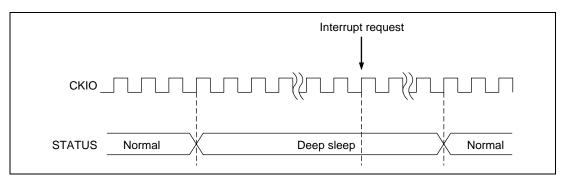

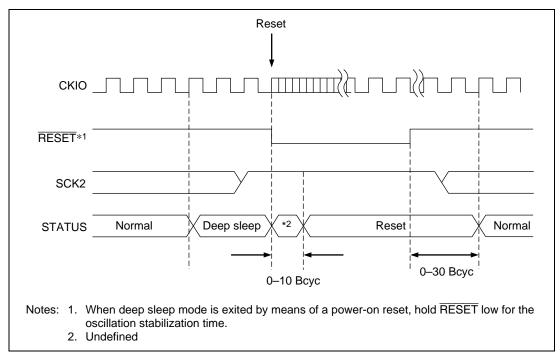

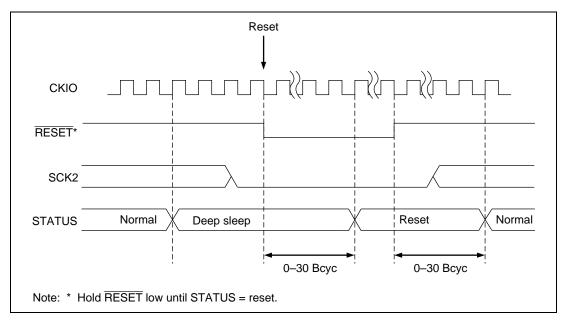

| 9.4 Deep Sleep Mode                                | 200 |

| 9.4.1 Transition to Deep Sleep Mode                | 200 |

| 9.4.2 Exit from Deep Sleep Mode                    | 200 |

| 9.5 Standby Mode                                   | 201 |

| 9.5.1 Transition to Standby Mode                   | 201 |

| 9.5.2 Exit from Standby Mode                       |     |

| 9.5.3 Clock Pause Function                         | 202 |

| 9.6 Module Standby Function                        | 203 |

| 9.6.1 Transition to Module Standby Function        | 203 |

| 9.6.2 Exit from Module Standby Function            |     |

| 9.7 STATUS Pin Change Timing                       |     |

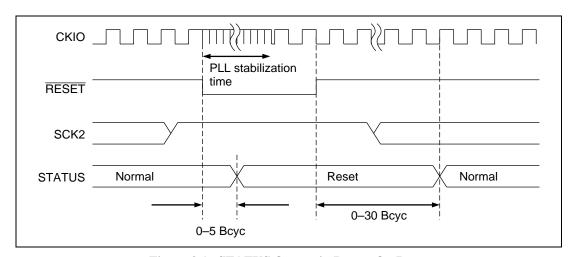

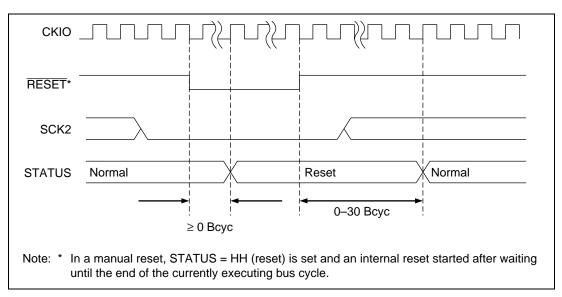

| 9.7.1 In Reset                                     |     |

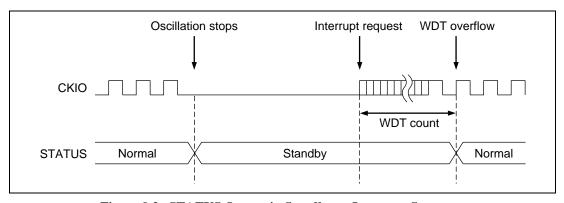

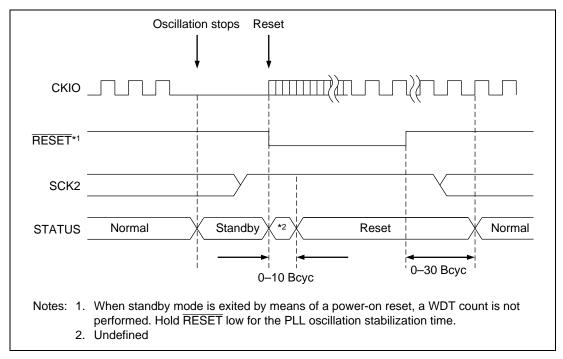

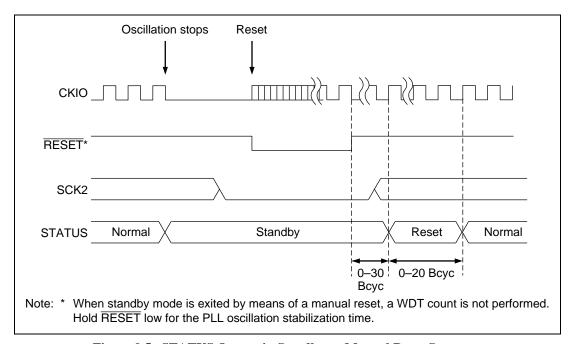

| 9.7.2 In Exit from Standby Mode                    |     |

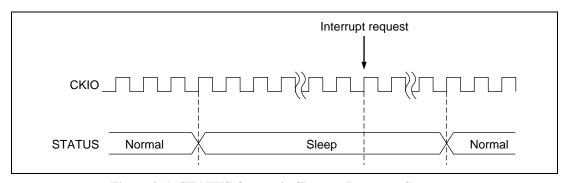

| 9.7.3 In Exit from Sleep Mode                      |     |

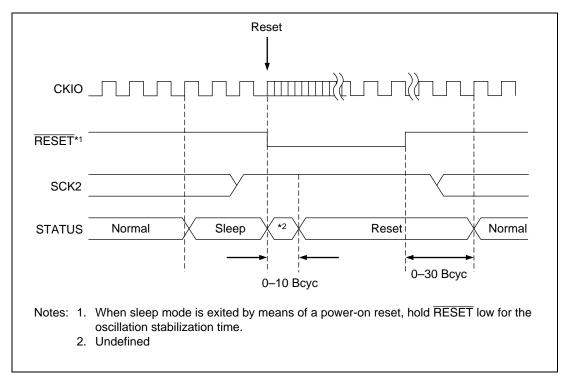

| 9.7.4 In Exit from Deep Sleep Mode                 | 210 |

| Section 10 Clock Oscillation Circuits              | 213 |

| 10.1 Overview                                      | 213 |

| 10.1.1 Features                                    | 213 |

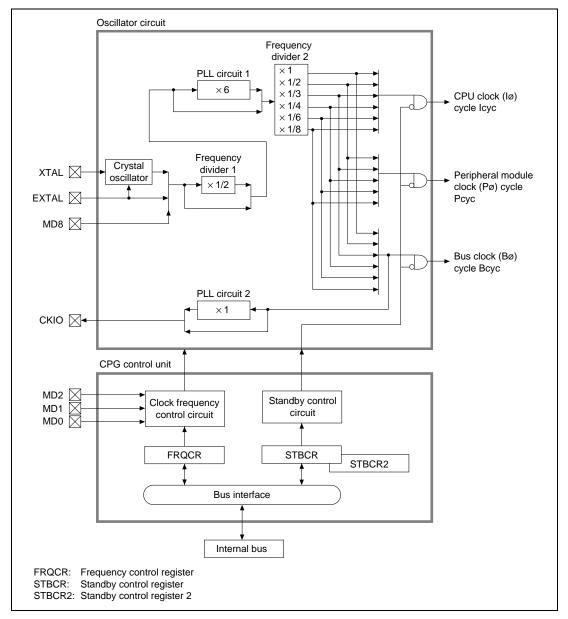

| 10.2 Overview of CPG                               | 215 |

| 10.2.1 Block Diagram of CPG                        | 215 |

| 10.2.2 CPG Pin Configuration                       | 217 |

| 10.2.3 CPG Register Configuration                  |     |

| 10.3 Clock Operating Modes                         | 218 |

| 10.4 CPG Register Description                                               | 220 |

|-----------------------------------------------------------------------------|-----|

| 10.4.1 Frequency Control Register (FRQCR)                                   | 220 |

| 10.5 Changing the Frequency                                                 |     |

| 10.5.1 Changing PLL Circuit 1 Starting/Stopping (When PLL Circuit 2 is Off) | 222 |

| 10.5.2 Changing PLL Circuit 1 Starting/Stopping (When PLL Circuit 2 is On)  | 223 |

| 10.5.3 Changing Bus Clock Division Ratio (When PLL Circuit 2 is On)         | 223 |

| 10.5.4 Changing Bus Clock Division Ratio (When PLL Circuit 2 is Off)        | 223 |

| 10.5.5 Changing CPU or Peripheral Module Clock Division Ratio               | 224 |

| 10.6 Output Clock Control                                                   | 224 |

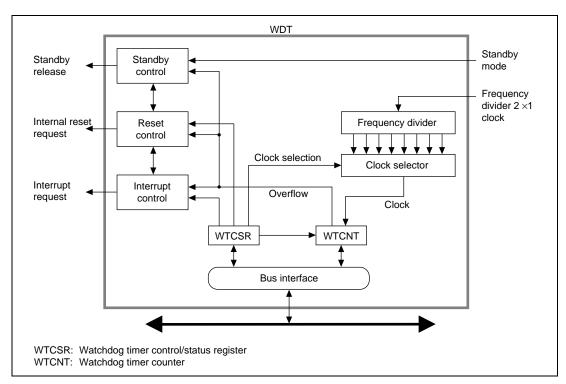

| 10.7 Overview of Watchdog Timer                                             | 224 |

| 10.7.1 Block Diagram                                                        | 224 |

| 10.7.2 Register Configuration                                               | 225 |

| 10.8 WDT Register Descriptions                                              | 225 |

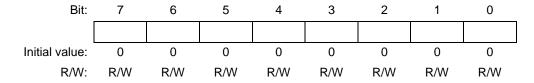

| 10.8.1 Watchdog Timer Counter (WTCNT)                                       | 225 |

| 10.8.2 Watchdog Timer Control/Status Register (WTCSR)                       | 226 |

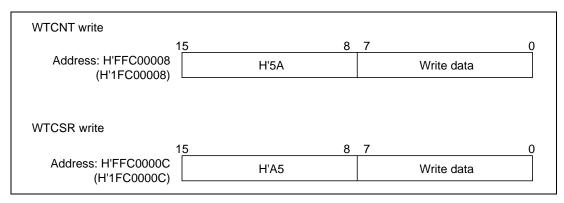

| 10.8.3 Notes on Register Access                                             | 228 |

| 10.9 Using the WDT                                                          | 229 |

| 10.9.1 Standby Clearing Procedure                                           | 229 |

| 10.9.2 Frequency Changing Procedure                                         | 229 |

| 10.9.3 Using Watchdog Timer Mode                                            | 230 |

| 10.9.4 Using Interval Timer Mode                                            | 230 |

| 10.10 Notes on Board Design                                                 | 231 |

| 11.1 Overview                                                               | 233 |

| 11.1.1 Features                                                             | 233 |

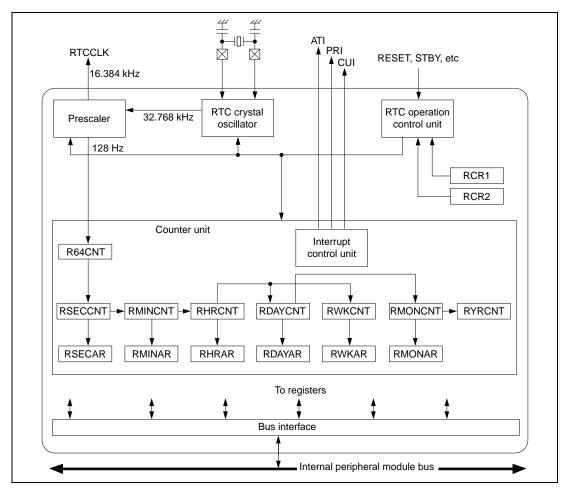

| 11.1.2 Block Diagram                                                        | 234 |

| 11.1.3 Pin Configuration.                                                   | 235 |

| 11.1.4 Register Configuration                                               | 235 |

| 11.2 Register Descriptions                                                  | 237 |

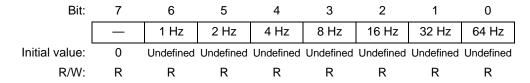

| 11.2.1 64 Hz Counter (R64CNT)                                               | 237 |

| 11.2.2 Second Counter (RSECCNT)                                             | 237 |

| 11.2.3 Minute Counter (RMINCNT)                                             | 238 |

| 11.2.4 Hour Counter (RHRCNT)                                                |     |

| 11.2.5 Day-of-Week Counter (RWKCNT)                                         | 239 |

| 11.2.6 Day Counter (RDAYCNT)                                                | 240 |

| 11.2.7 Month Counter (RMONCNT)                                              | 241 |

| 11.2.8 Year Counter (RYRCNT)                                                | 242 |

| 11.2.9 Second Alarm Register (RSECAR)                                       | 243 |

| 11.2.10 Minute Alarm Register (RMINAR)                                      |     |

| 11.2.11 Hour Alarm Register (RHRAR)                                         |     |

| 11.2.12 Day-of-Week Alarm Register (RWKAR)                                  |     |

| 11.2.13 Day Alarm Register (RDAYAR)                                         |     |

| 11.2.14 Month Alarm Register (RMONAR)                                       | 248 |

| 11.2.15 RTC Control Register 1 (RCR1)                                       | 249 |

Rev. 2.0, 02/99, page v of xii

| 11.2.16 RTC Control Register 2 (RCR2)       | . 251 |

|---------------------------------------------|-------|

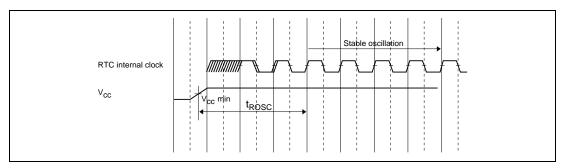

| 11.3 Operation                              | . 253 |

| 11.3.1 Time Setting Procedures              | . 253 |

| 11.3.2 Time Reading Procedures              | . 254 |

| 11.3.3 Alarm Function                       | . 255 |

| 11.4 Interrupts                             | . 256 |

| 11.5 Usage Notes                            | . 256 |

| 11.5.1 Register Initialization              | . 256 |

| 11.5.2 Crystal Oscillator Circuit           | . 256 |

| 12.1 Overview                               | . 259 |

| 12.1.1 Features                             | . 259 |

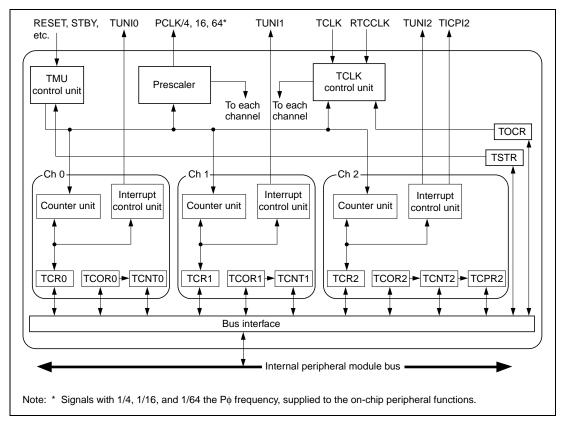

| 12.1.2 Block Diagram                        | . 260 |

| 12.1.3 Pin Configuration.                   | . 260 |

| 12.1.4 Register Configuration               | . 261 |

| 12.2 Register Descriptions                  | . 262 |

| 12.2.1 Timer Output Control Register (TOCR) | . 262 |

| 12.2.2 Timer Start Register (TSTR)          |       |

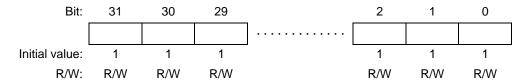

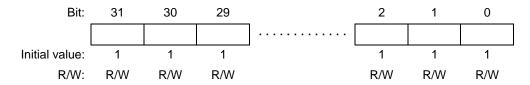

| 12.2.3 Timer Constant Registers (TCOR)      | . 264 |

| 12.2.4 Timer Counters (TCNT)                |       |

| 12.2.5 Timer Control Registers (TCR)        | . 265 |

| 12.2.6 Input Capture Register (TCPR2)       | . 268 |

| 12.3 Operation                              | . 269 |

| 12.3.1 Counter Operation                    | . 269 |

| 12.3.2 Input Capture Function               |       |

| 12.4 Interrupts                             | . 274 |

| 12.5 Usage Notes                            | . 275 |

| 12.5.1 Register Writes                      | . 275 |

| 12.5.2 TCNT Register Reads                  | . 275 |

| 12.5.3 Resetting the RTC Frequency Divider  | . 275 |

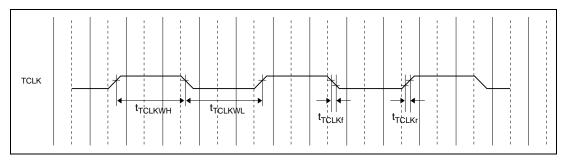

| 12.5.4 External Clock Frequency             | . 275 |

| G 2 10 D G 2 G 2 H (DGG)                    | 277   |

| Section 13 Bus State Controller (BSC)       |       |

| 13.1 Overview                               |       |

| 13.1.1 Features                             |       |

| 13.1.2 Block Diagram                        |       |

| 13.1.3 Pin Configuration.                   |       |

| 13.1.4 Register Configuration               |       |

| 13.1.5 Overview of Areas                    |       |

| 13.1.6 PCMCIA Support                       |       |

| 13.2 Register Descriptions                  |       |

| 13.2.1 Bus Control Register 1 (BCR1)        |       |

| 13.2.2 Bus Control Register 2 (BCR2)        |       |

| 13.2.3 Wait Control Register 1 (WCR1)       | . 300 |

| 13.2.4 Wait Control Register 2 (WCR2)                     | 303 |

|-----------------------------------------------------------|-----|

| 13.2.5 Wait Control Register 3 (WCR3)                     |     |

| 13.2.6 Memory Control Register (MCR)                      | 313 |

| 13.2.7 PCMCIA Control Register (PCR)                      | 320 |

| 13.2.8 Synchronous DRAM Mode Register (SDMR)              | 323 |

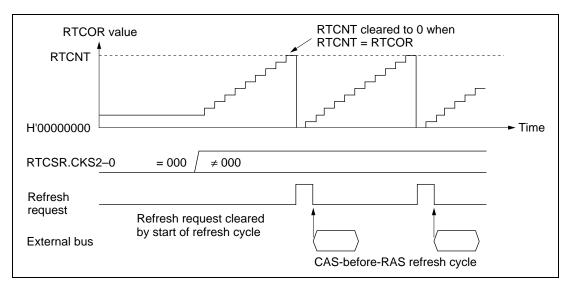

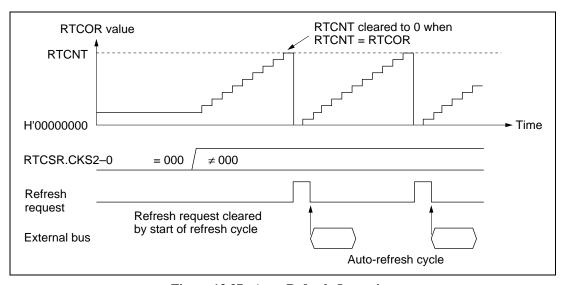

| 13.2.9 Refresh Timer Control/Status Register (RTSCR)      | 325 |

| 13.2.10 Refresh Timer Counter (RTCNT)                     | 327 |

| 13.2.11 Refresh Time Constant Register (RTCOR)            | 328 |

| 13.2.12 Refresh Count Register (RFCR)                     | 329 |

| 13.2.13 Notes on Accessing Refresh Control Registers      | 330 |

| 13.3 Operation                                            | 331 |

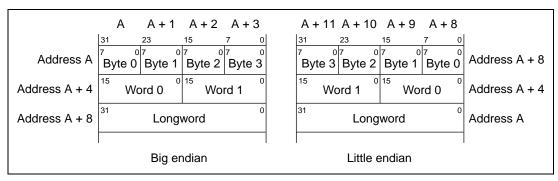

| 13.3.1 Endian/Access Size and Data Alignment              |     |

| 13.3.2 Areas                                              |     |

| 13.3.3 Basic Interface                                    | 347 |

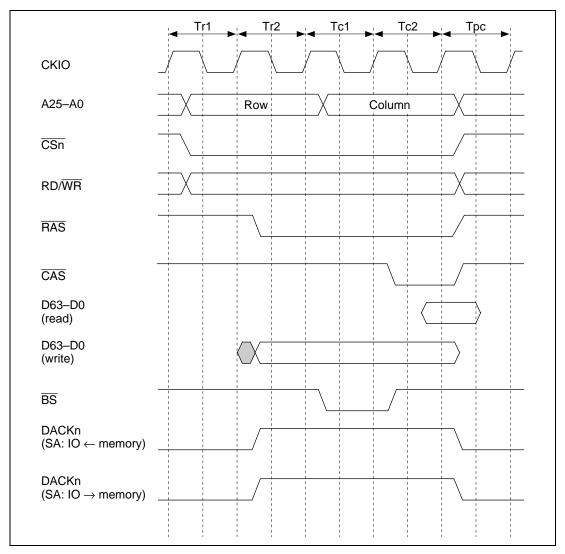

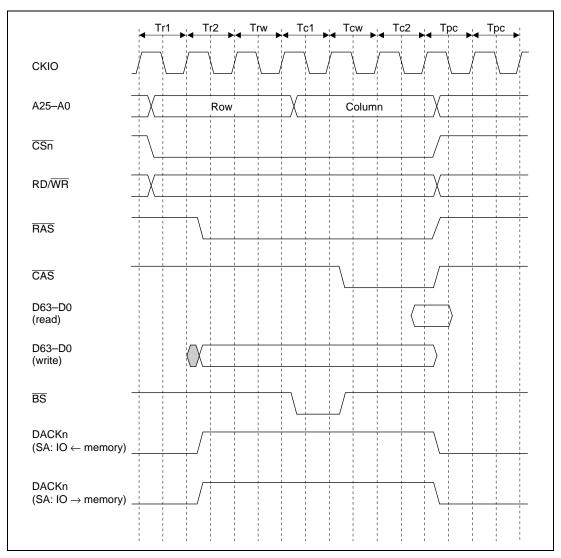

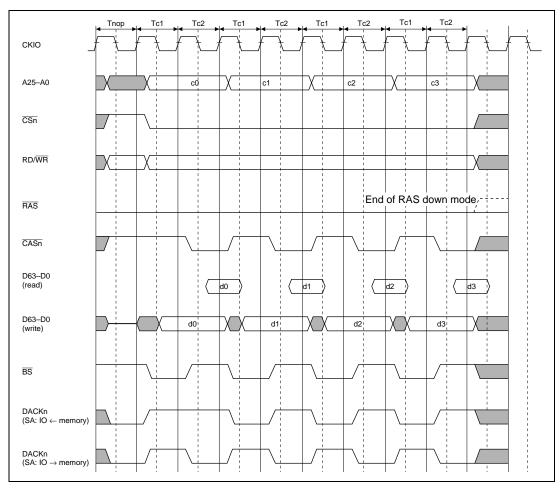

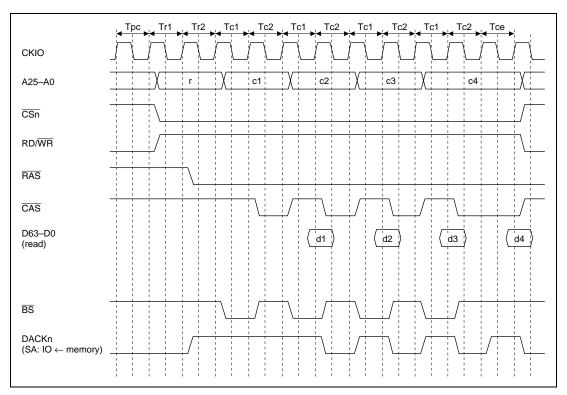

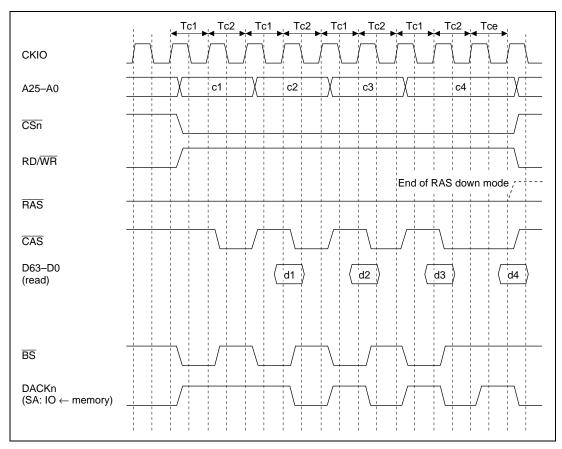

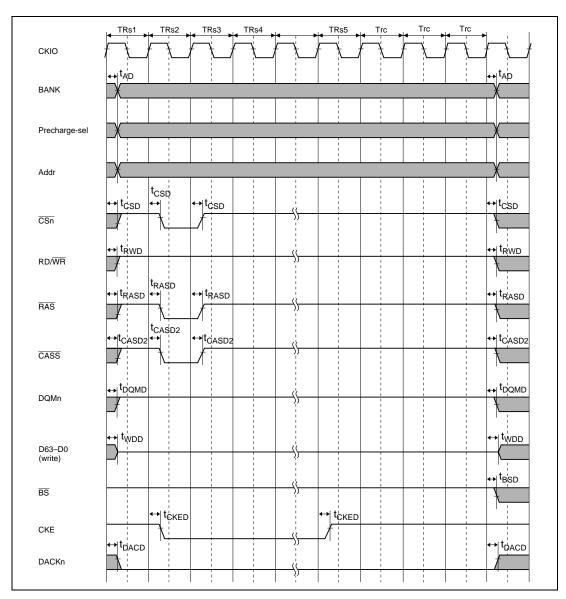

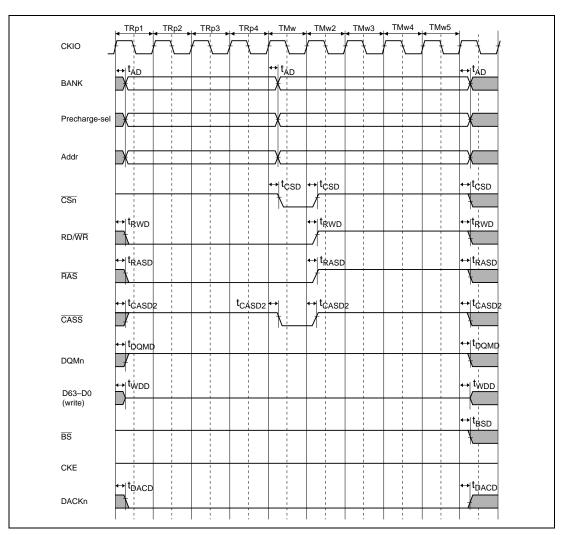

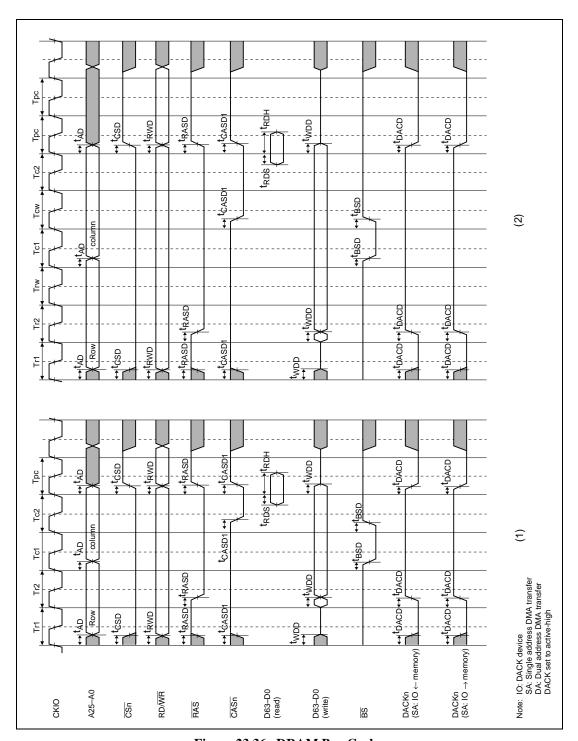

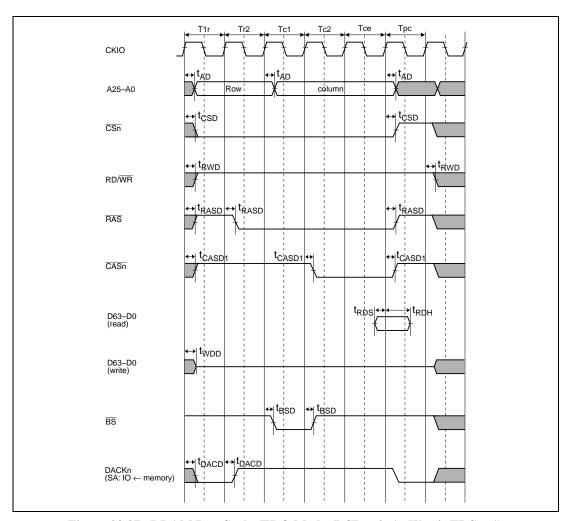

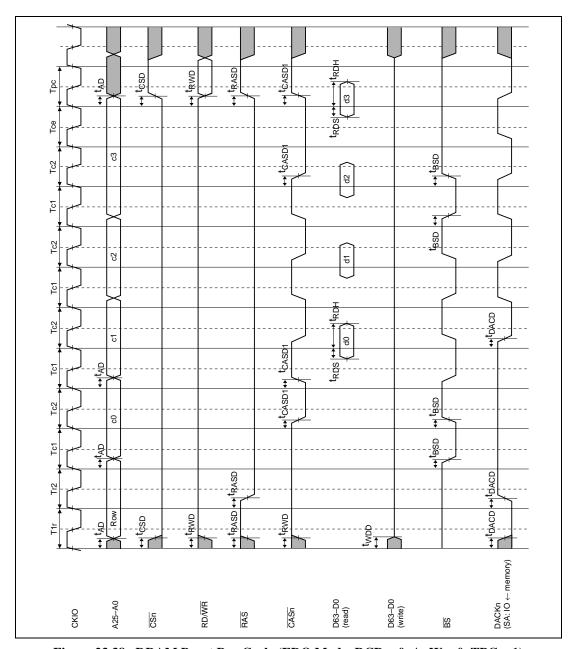

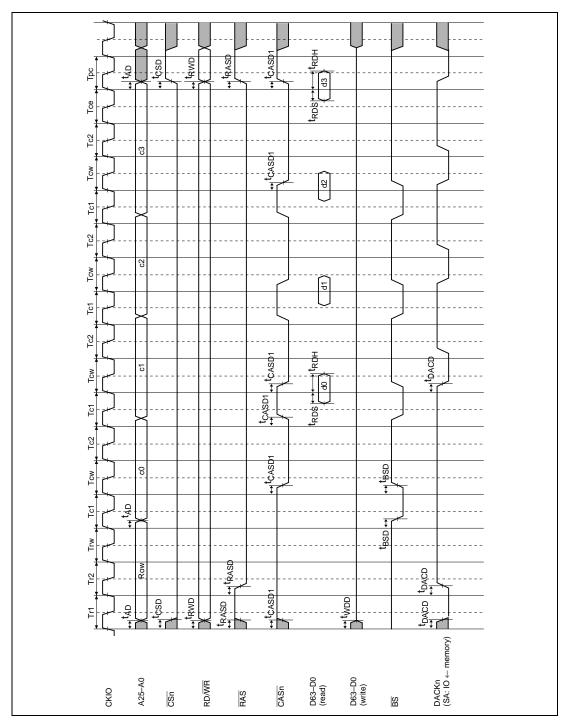

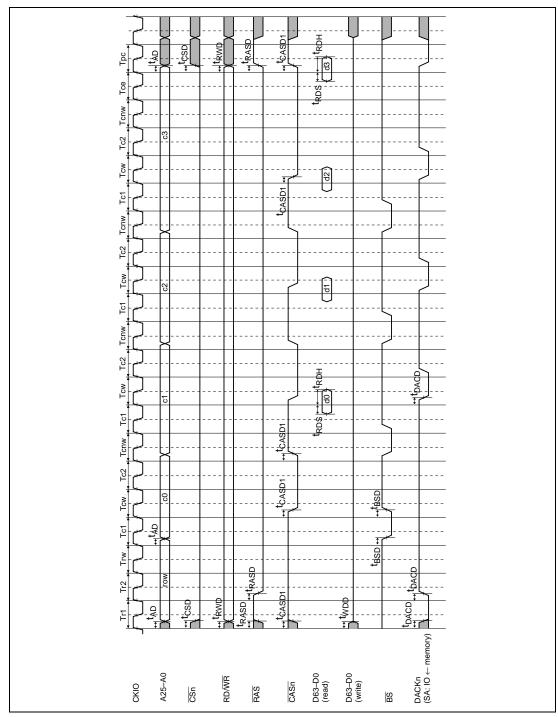

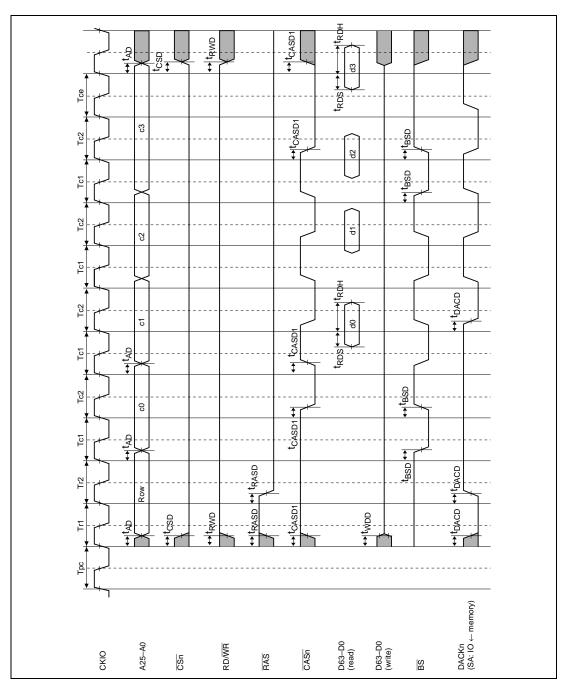

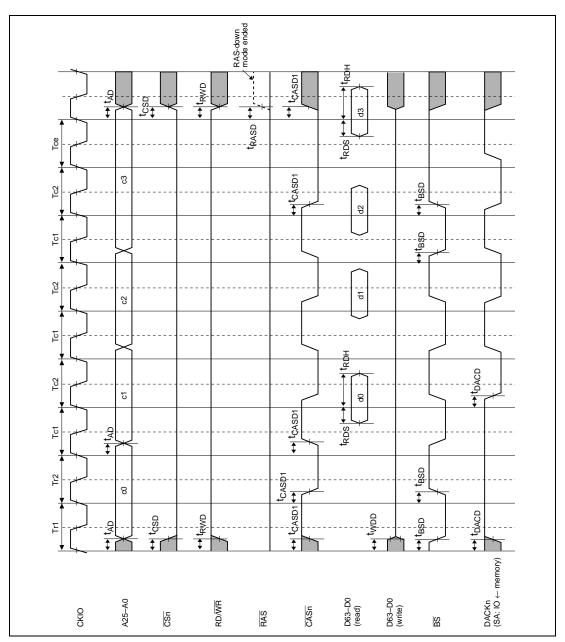

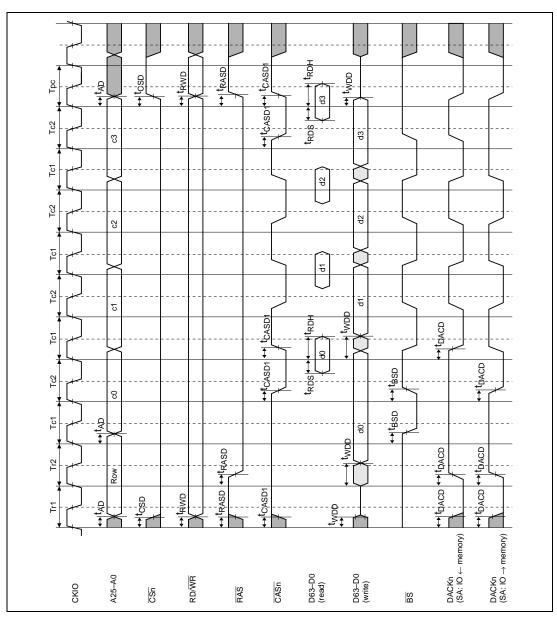

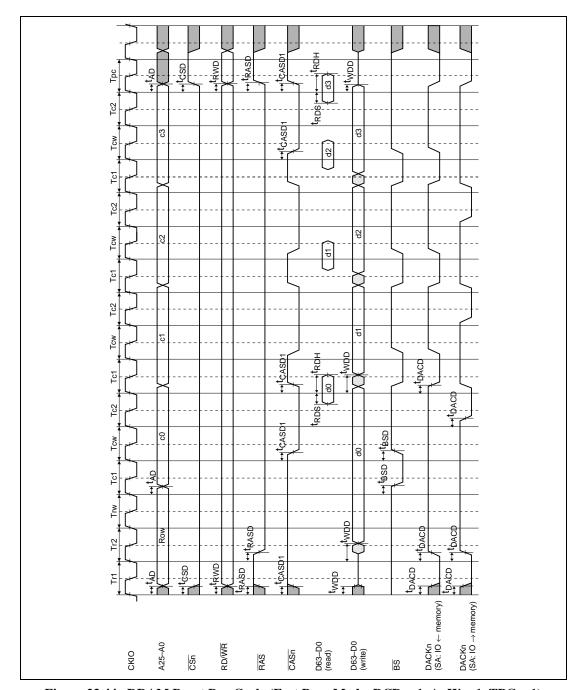

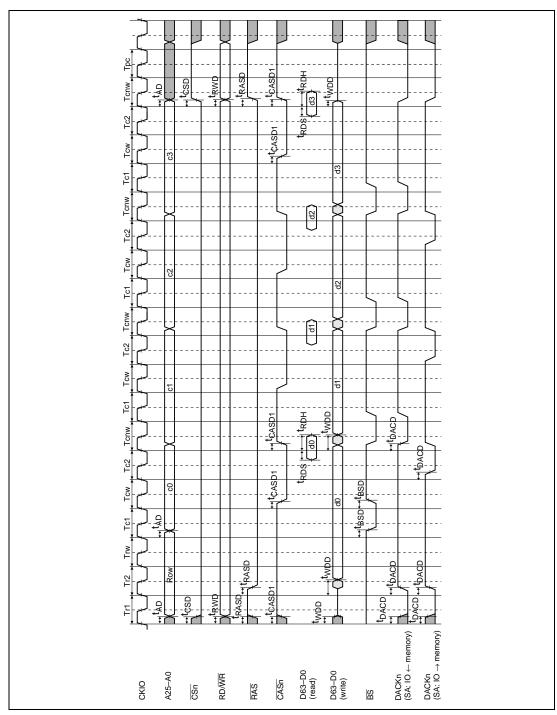

| 13.3.4 DRAM Interface                                     | 355 |

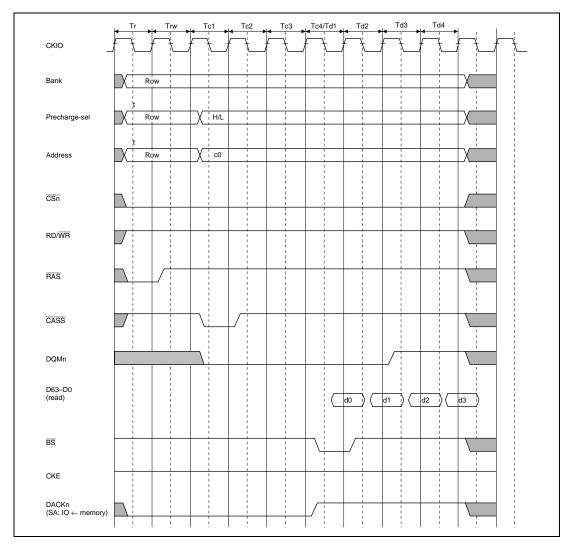

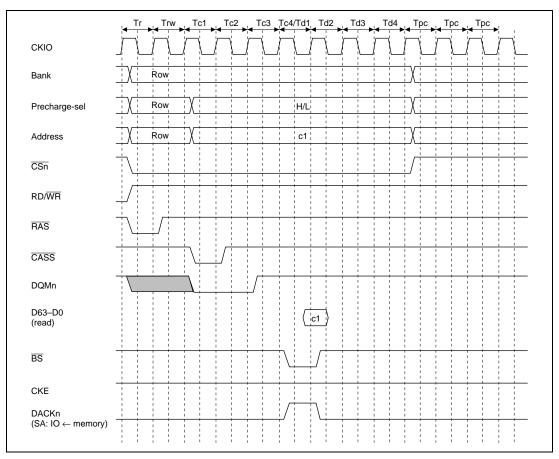

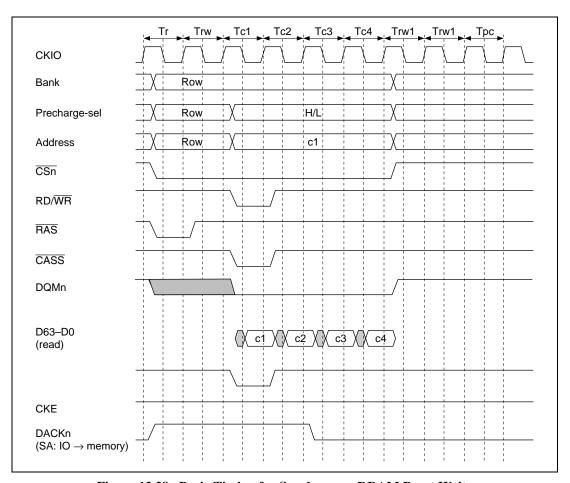

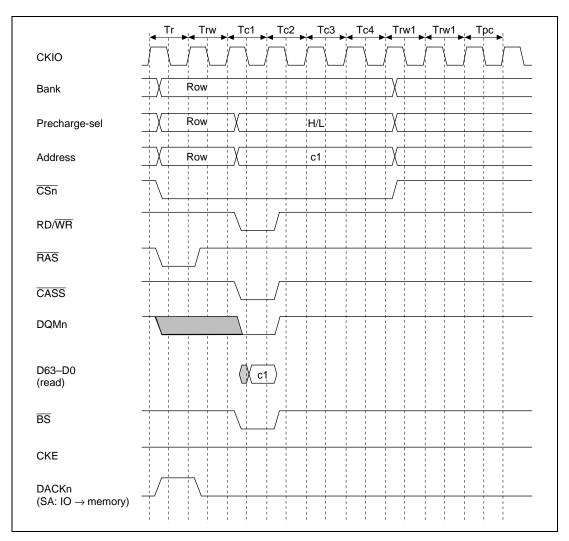

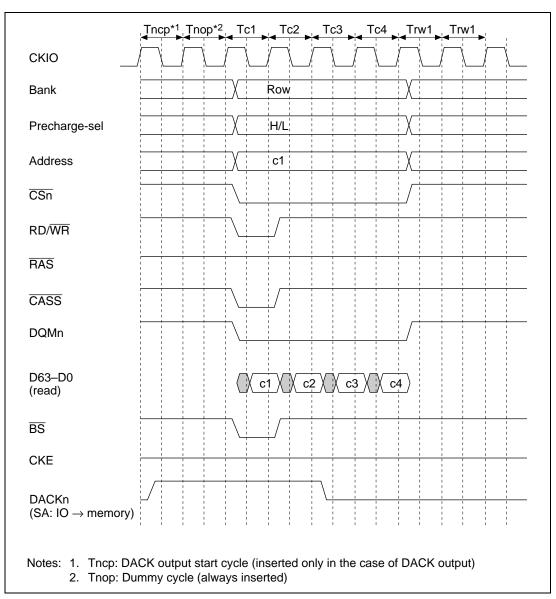

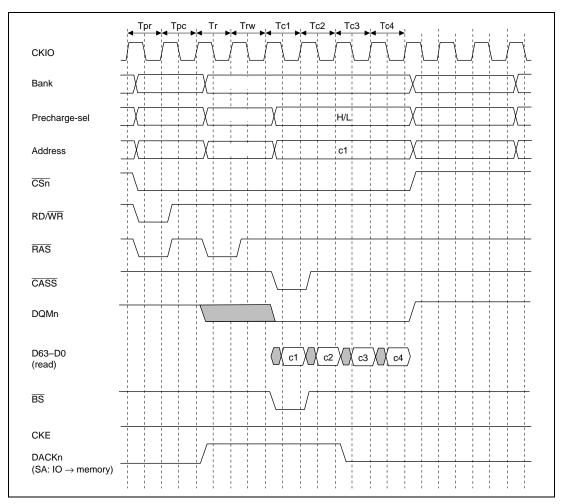

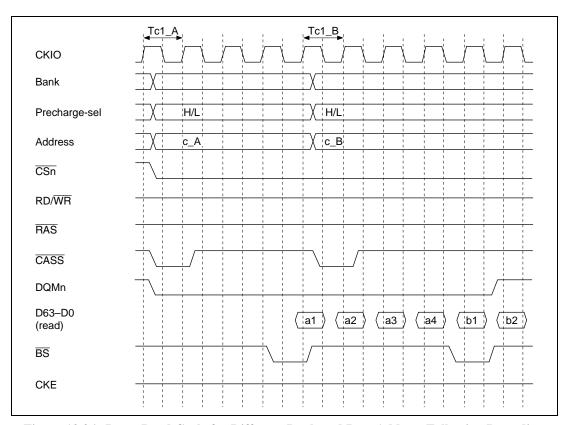

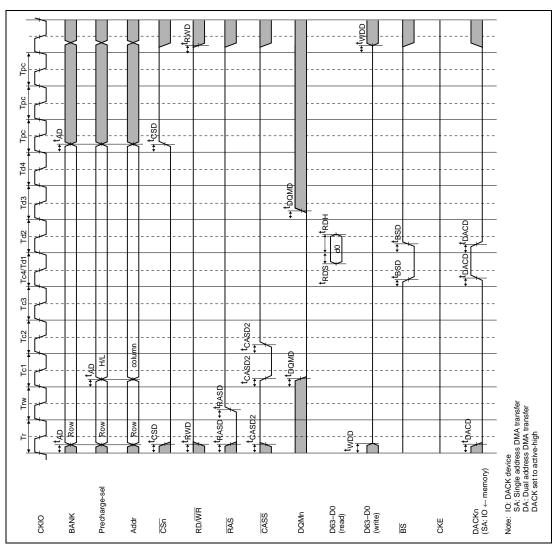

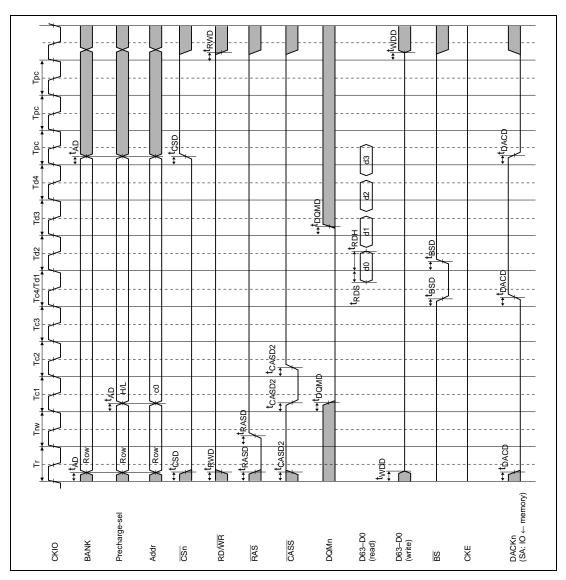

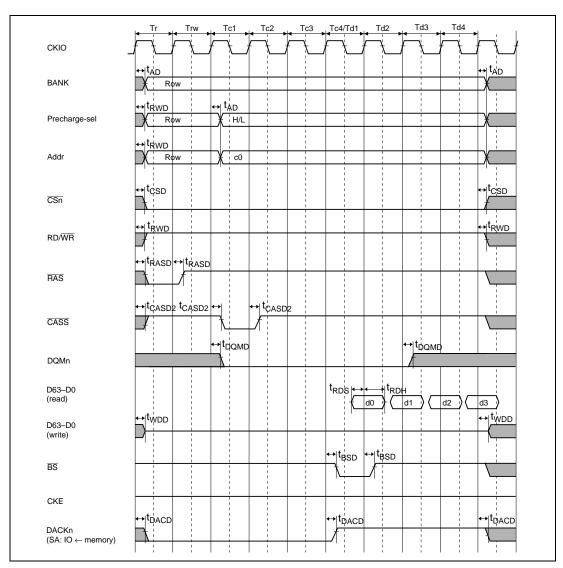

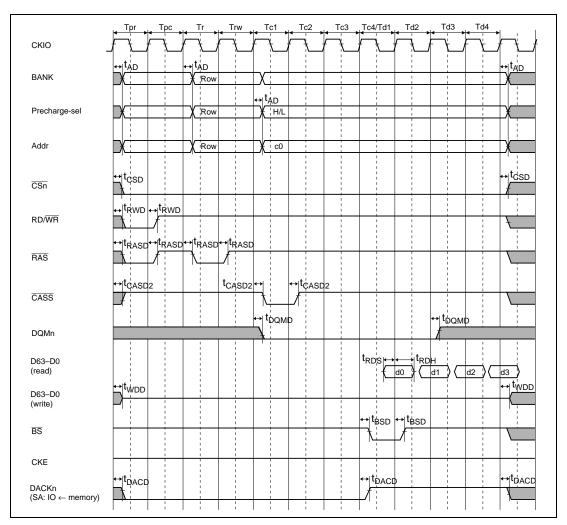

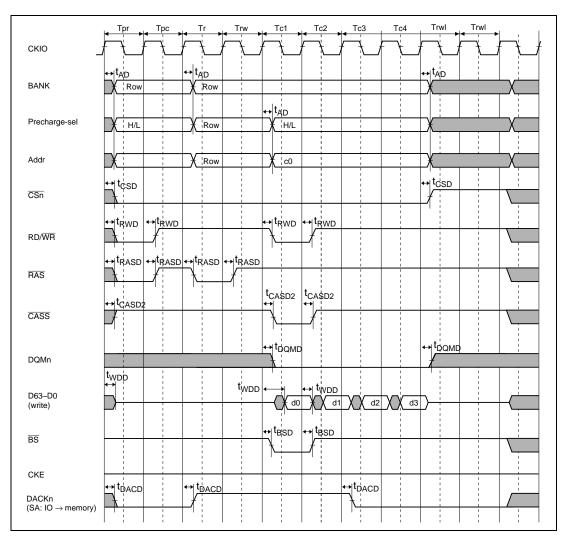

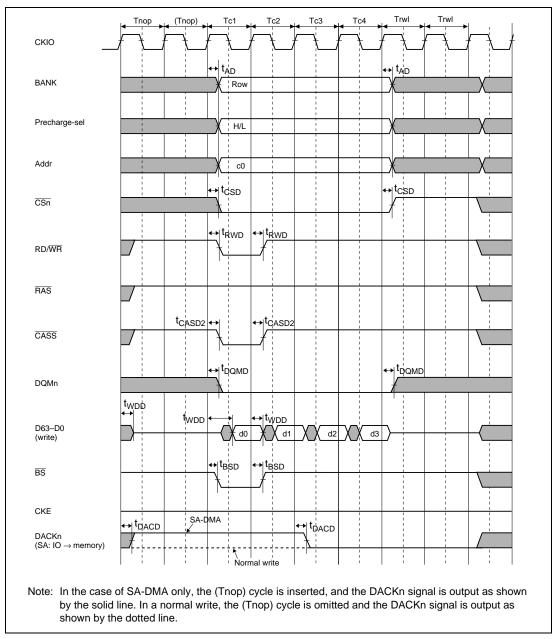

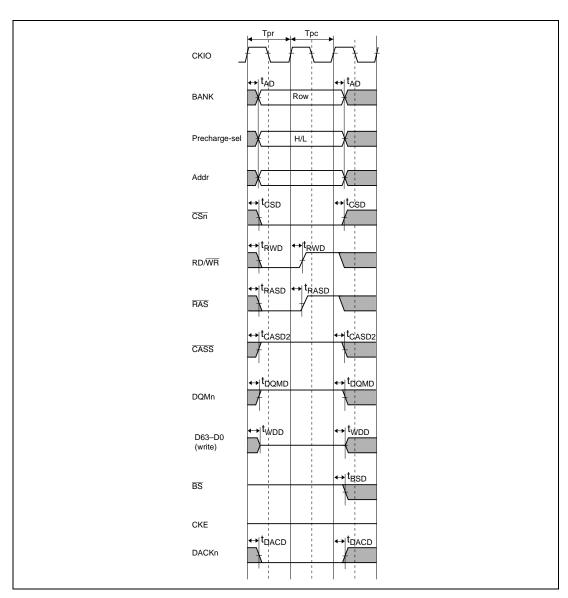

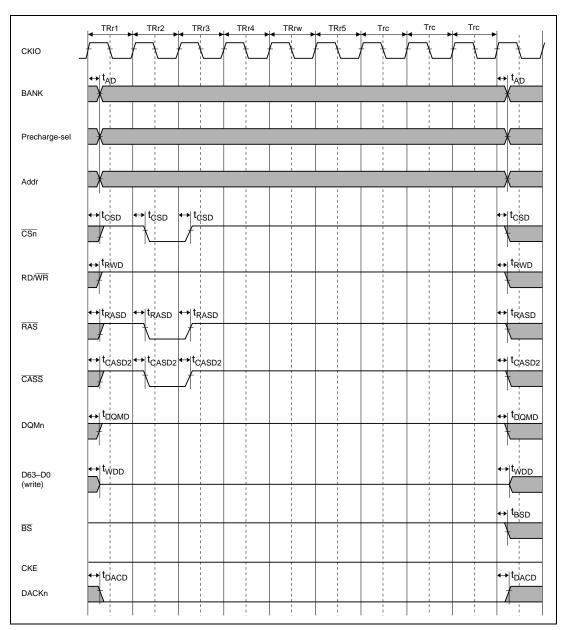

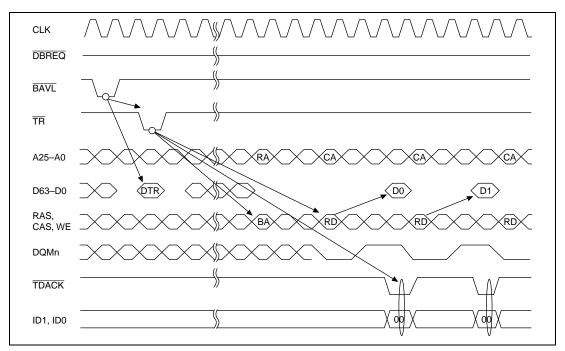

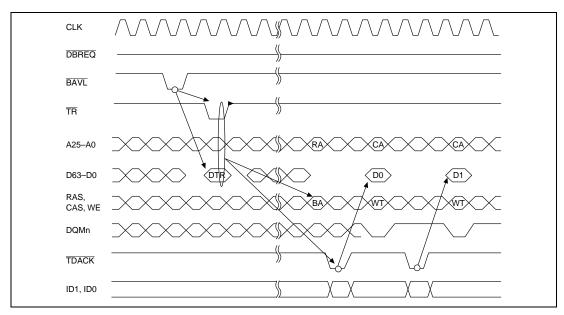

| 13.3.5 Synchronous DRAM Interface                         | 372 |

| 13.3.6 Burst ROM Interface                                | 396 |

| 13.3.7 PCMCIA Interface                                   | 399 |

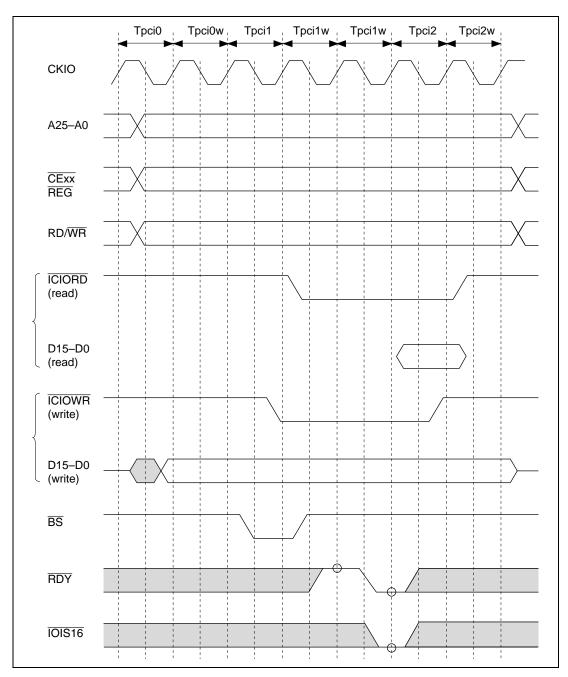

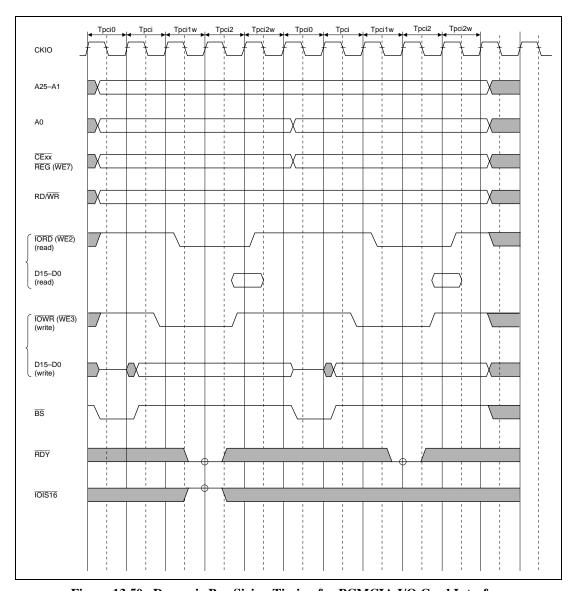

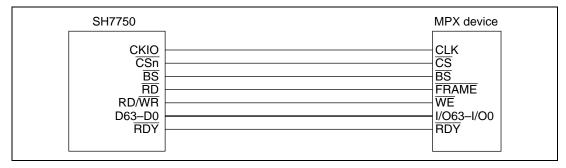

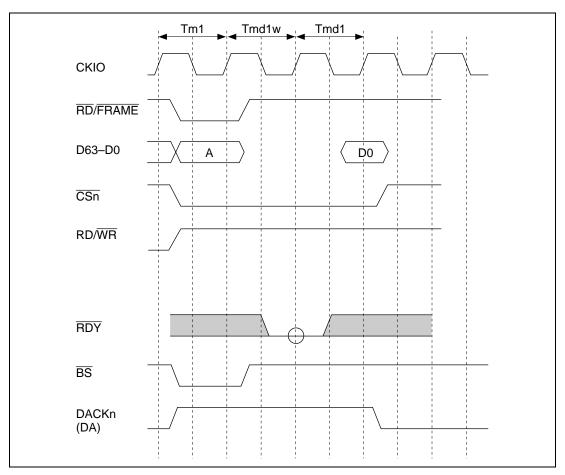

| 13.3.8 MPX Interface                                      | 408 |

| 13.3.9 Byte Control SRAM                                  | 415 |

| 13.3.10 Waits between Access Cycles                       |     |

| 13.3.11 Bus Arbitration                                   |     |

| 13.3.12 Master Mode                                       | 424 |

| 13.3.13 Slave Mode                                        | 425 |

| 13.3.14 Partial-Sharing Master Mode                       | 426 |

| 13.3.15 Cooperation between Master and Slave              |     |

| Section 14 Direct Memory Access Controller (DMAC)         | 429 |

| 14.1 Overview                                             |     |

| 14.1.1 Features                                           | 429 |

| 14.1.2 Block Diagram                                      | 431 |

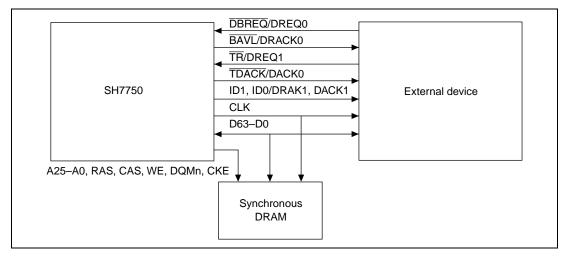

| 14.1.3 Pin Configuration                                  | 432 |

| 14.1.4 Register Configuration                             |     |

| 14.2 Register Descriptions                                | 435 |

| 14.2.1 DMA Source Address Registers 0–3 (SAR0–SAR3)       | 435 |

| 14.2.2 DMA Destination Address Registers 0–3 (DAR0–DAR3)  |     |

| 14.2.3 DMA Transfer Count Registers 0–3 (DMATCR0–DMATCR3) | 437 |

| 14.2.4 DMA Channel Control Registers 0–3 (CHCR0–CHCR3)    |     |

| 14.2.5 DMA Operation Register (DMAOR)                     |     |

| 14.3 Operation                                            |     |

| 14.3.1 DMA Transfer Procedure                             |     |

| 14.3.2 DMA Transfer Requests                              |     |

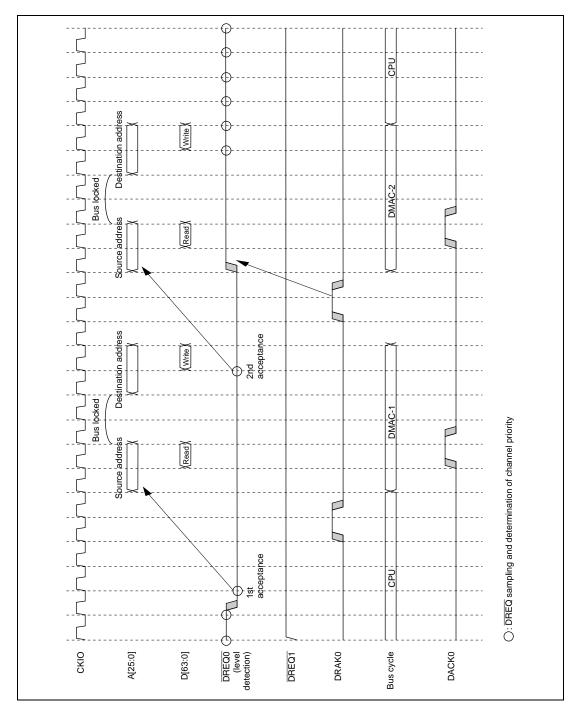

| 14 3 3 Channel Priorities                                 |     |

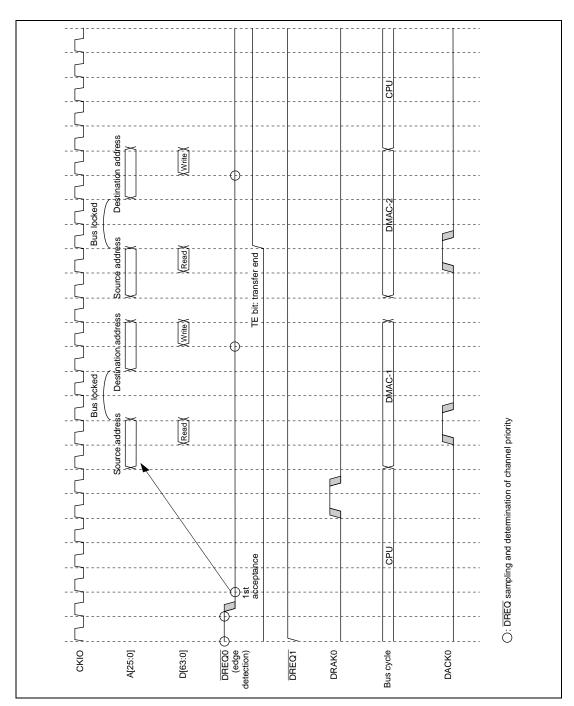

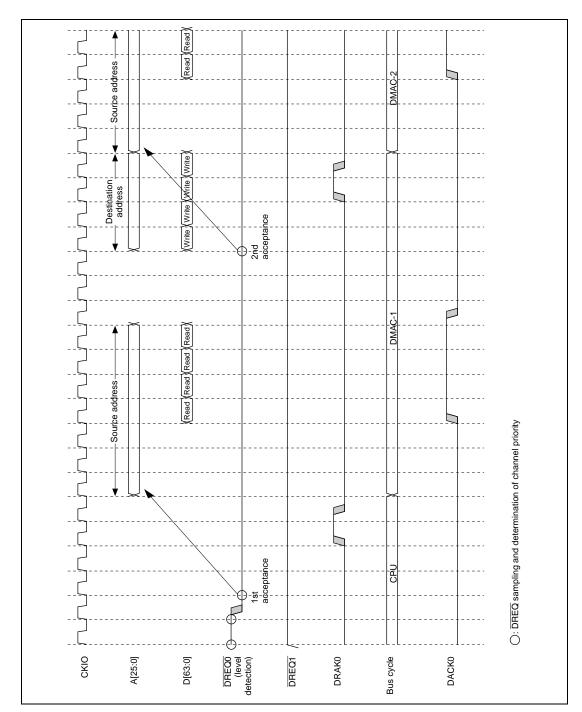

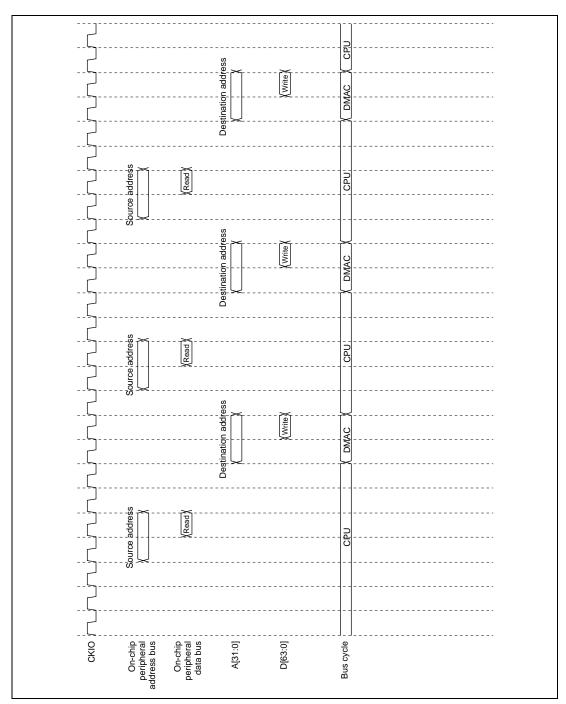

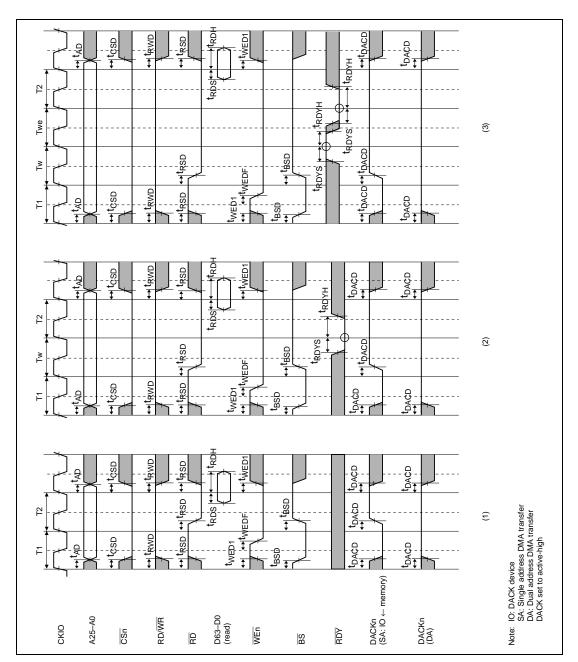

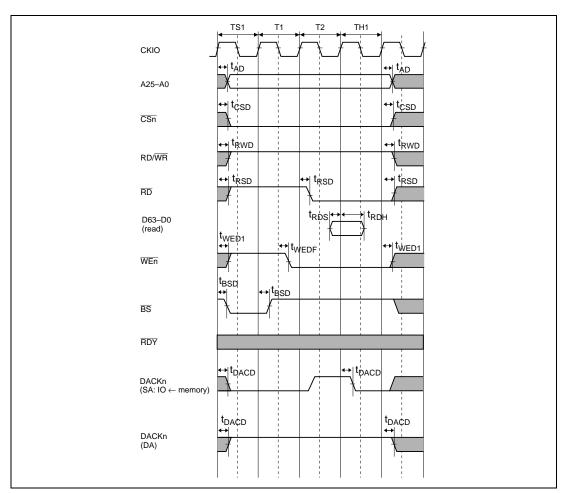

| 14.3.4 Types of DMA Transfer                                                 | 456  |

|------------------------------------------------------------------------------|------|

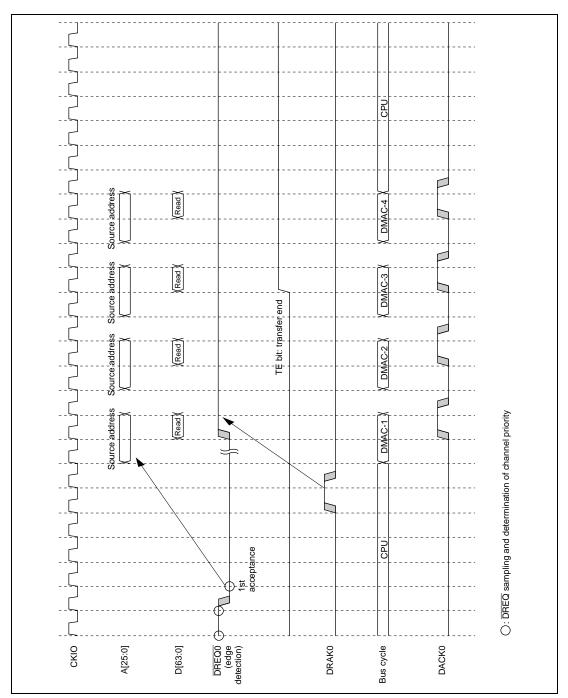

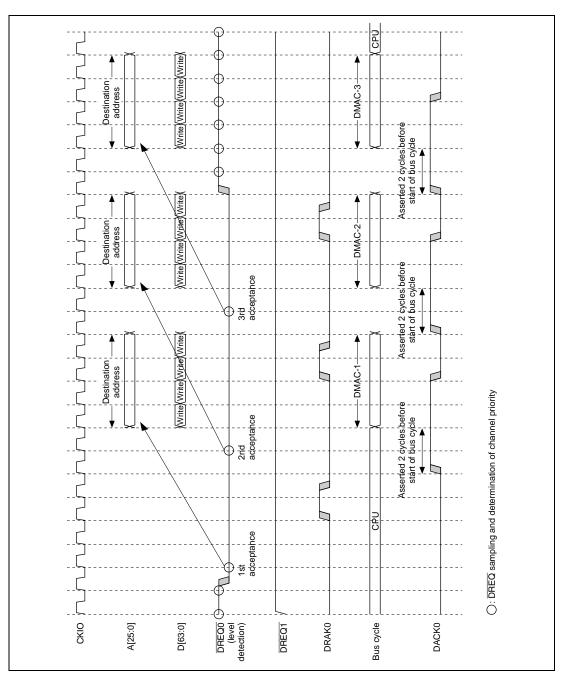

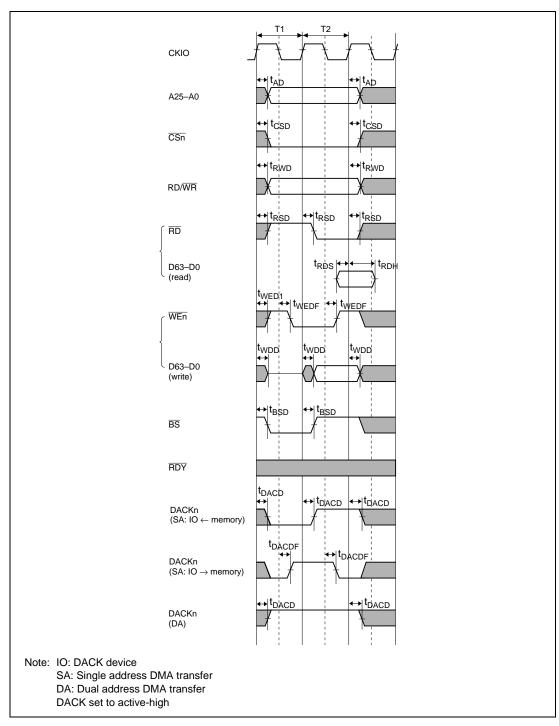

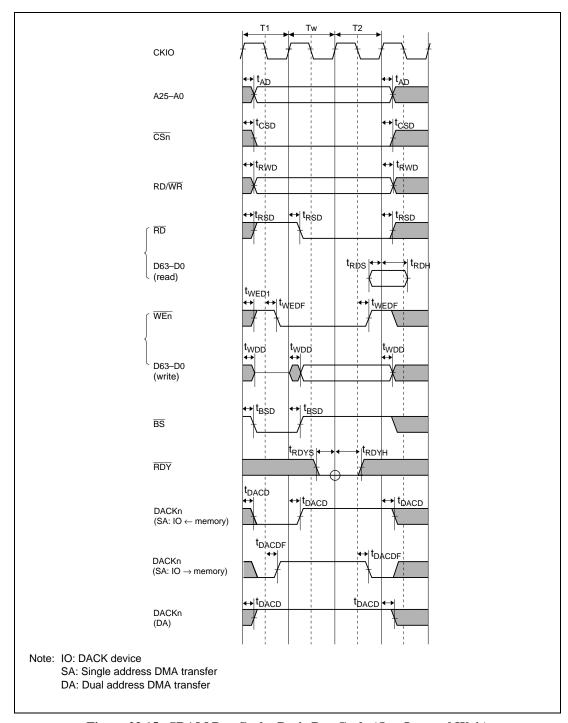

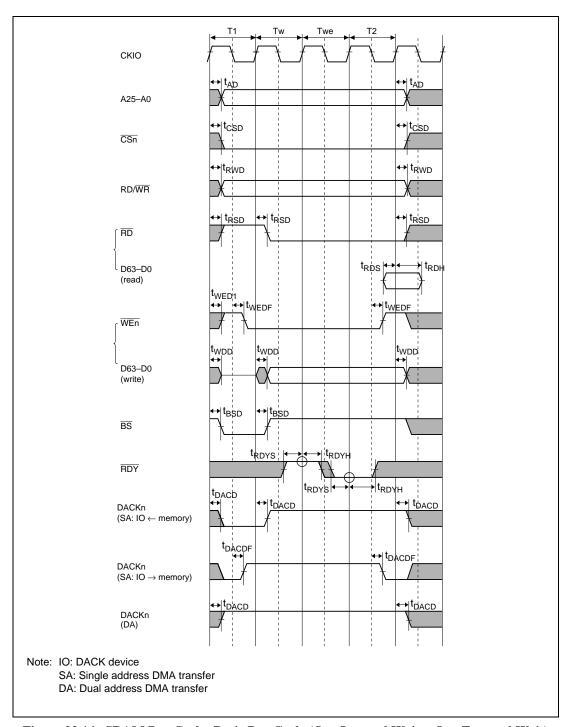

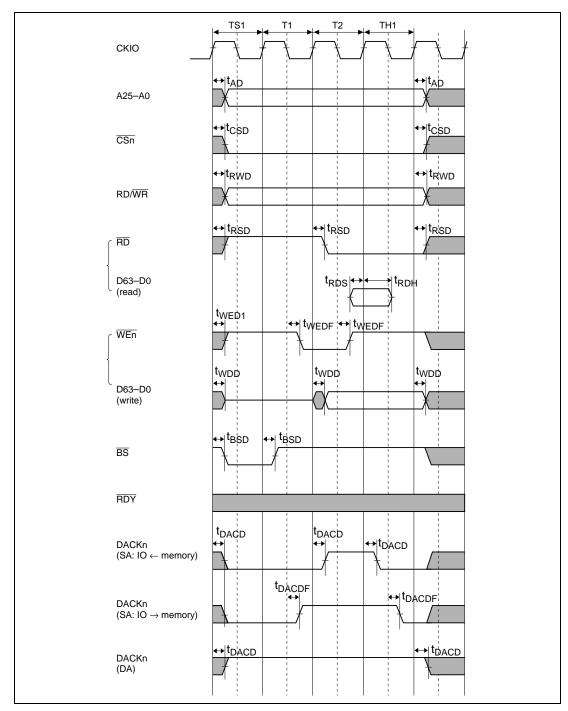

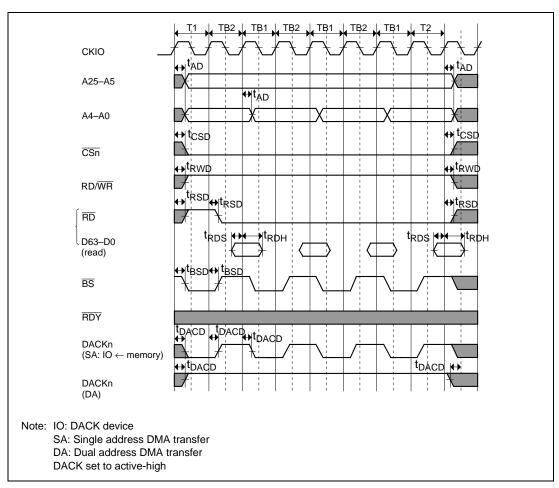

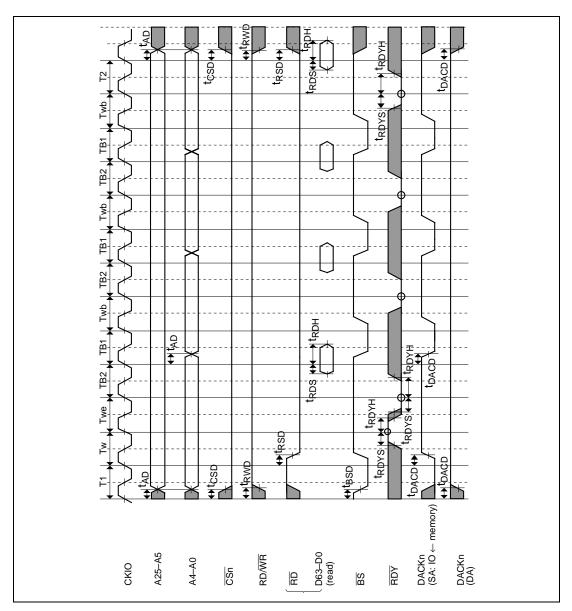

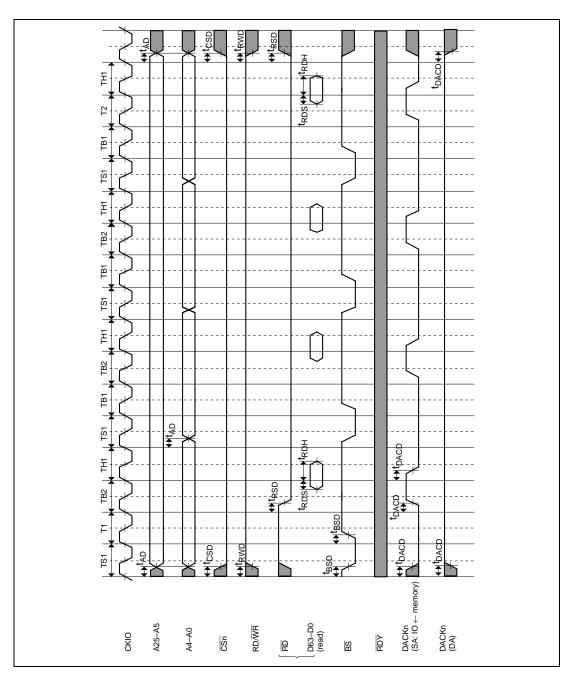

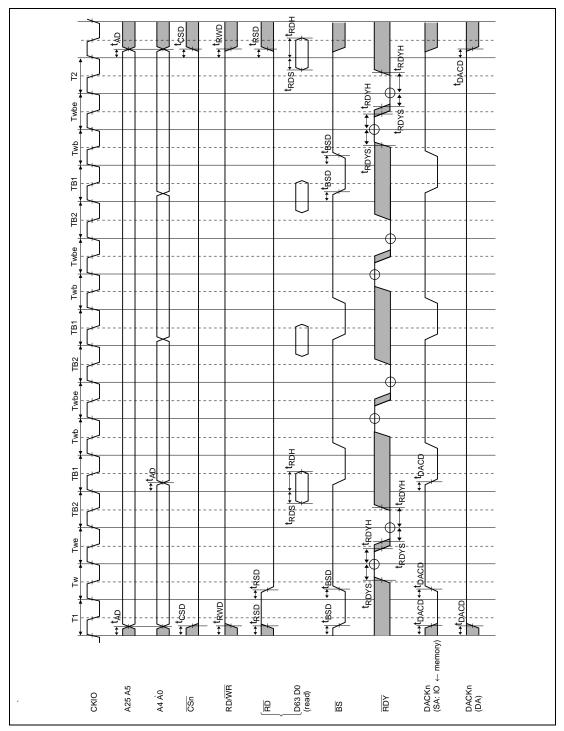

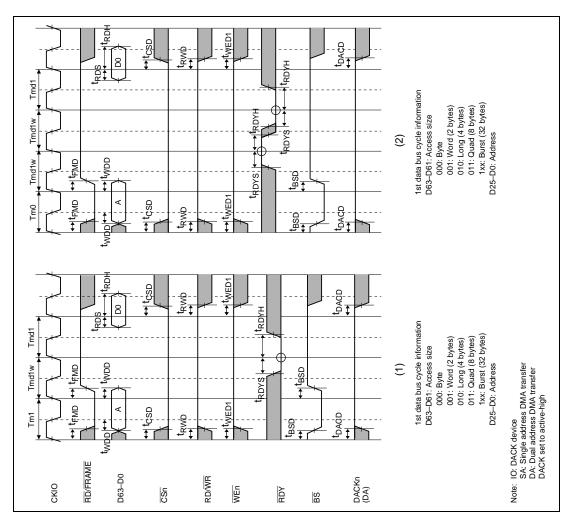

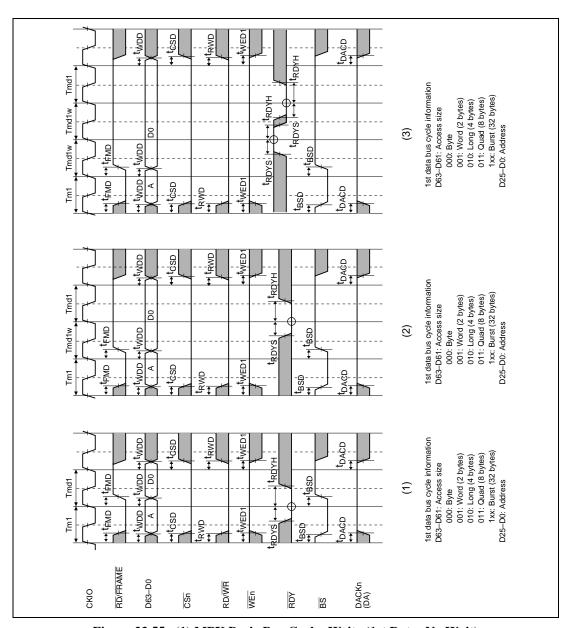

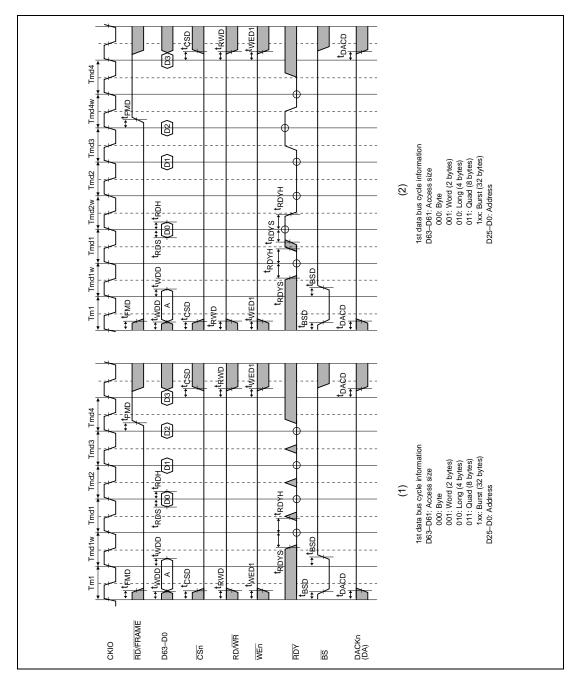

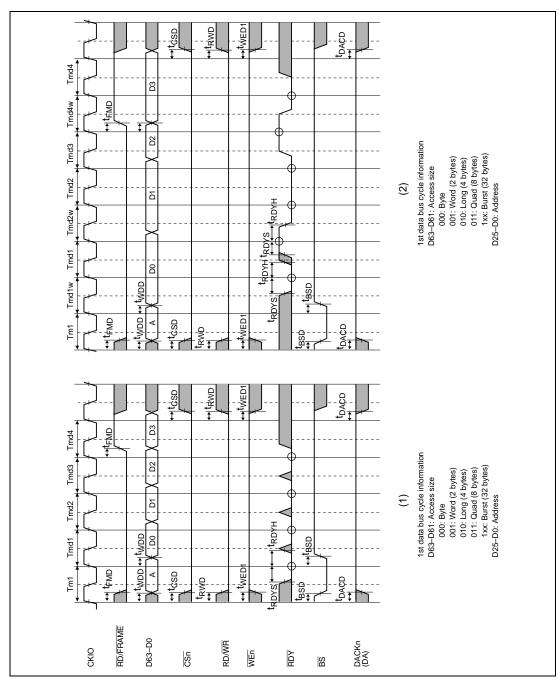

| 14.3.5 Number of Bus Cycle States and DREQ Pin Sampling Timing               | 464  |

| 14.3.6 Ending DMA Transfer                                                   | 479  |

| 14.4 Examples of Use                                                         | 482  |

| 14.4.1 Examples of Transfer between External Memory and an External Device w | vith |

| DACK .482                                                                    |      |

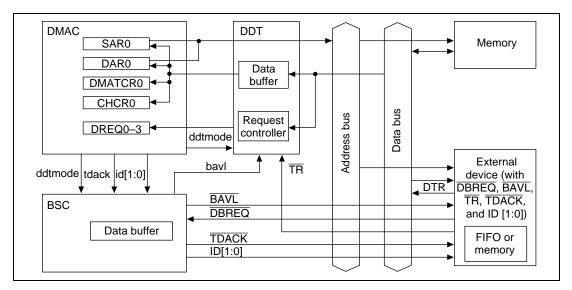

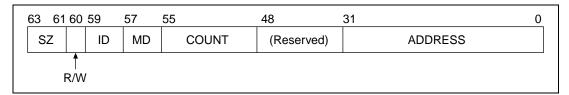

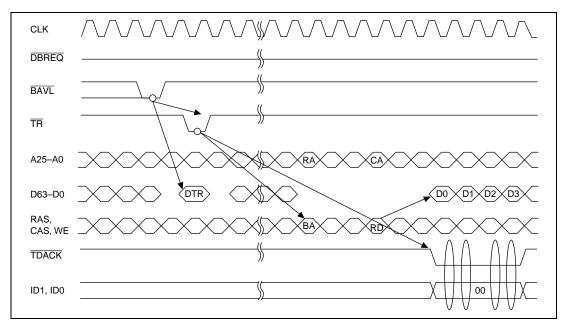

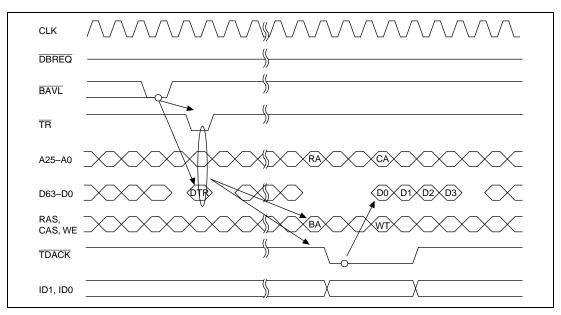

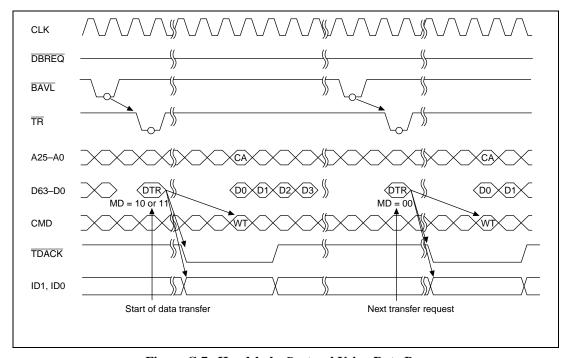

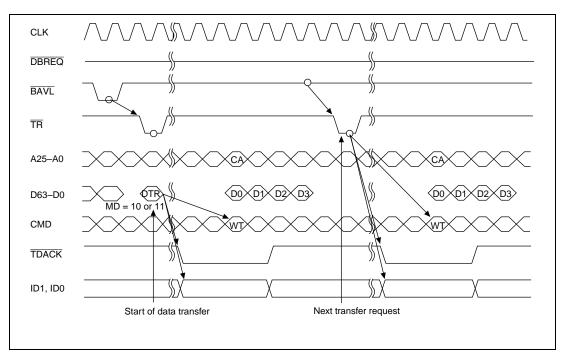

| 14.5 On-Demand Data Transfer Mode                                            | 483  |

| 14.5.1 Operation                                                             |      |

| 14.5.2 Notes on Use of DDT Module                                            | 485  |

| 14.6 Usage Notes                                                             | 487  |

| Section 15 Social Communication Intenfers (SCI)                              | 490  |

| Section 15 Serial Communication Interface (SCI)                              |      |

| 15.1 Overview                                                                |      |

| 15.1.1 Features                                                              |      |

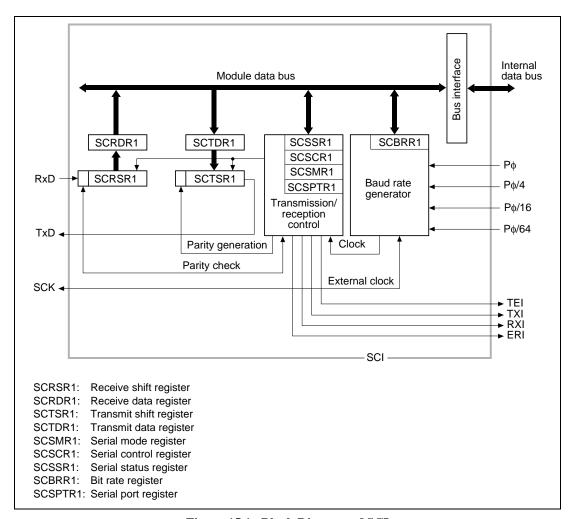

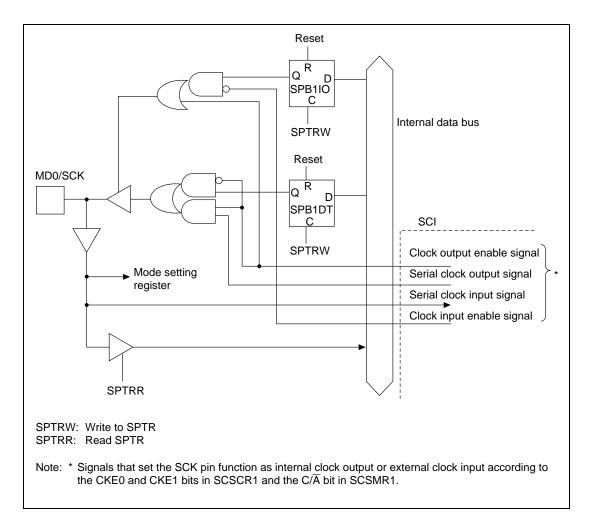

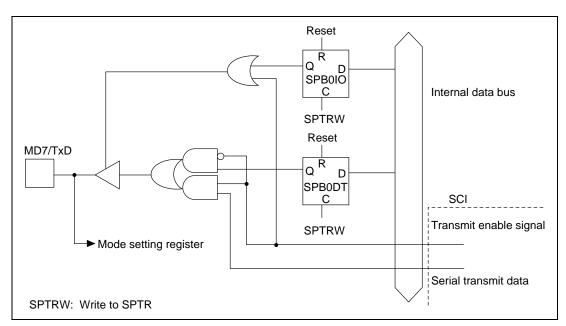

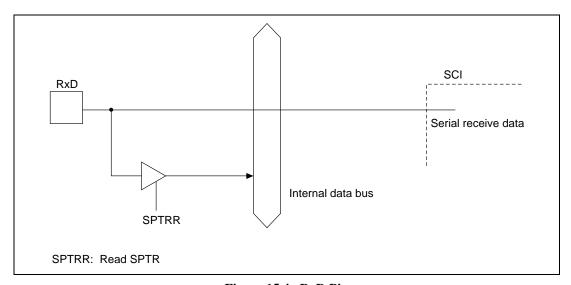

| 15.1.2 Block Diagram.                                                        |      |

| 15.1.3 Pin Configuration.                                                    |      |

| 15.1.4 Register Configuration.                                               |      |

| 15.2 Register Descriptions                                                   |      |

| 15.2.1 Receive Shift Register (SCRSR1)                                       |      |

| 15.2.2 Receive Data Register (SCRDR1)                                        |      |

| 15.2.3 Transmit Shift Register (SCTSR1)                                      |      |

| 15.2.4 Transmit Data Register (SCTDR1)                                       |      |

| 15.2.5 Serial Mode Register (SCSMR1)                                         |      |

| 15.2.6 Serial Control Register (SCSCR1)                                      |      |

| 15.2.7 Serial Status Register (SCSSR1)                                       |      |

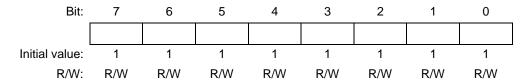

| 15.2.8 Serial Port Register (SCSPTR1)                                        |      |

| 15.2.9 Bit Rate Register (SCBRR1)                                            |      |

| 15.3 Operation                                                               |      |

| 15.3.1 Overview                                                              |      |

| 15.3.2 Operation in Asynchronous Mode                                        |      |

| 15.3.3 Multiprocessor Communication Function                                 |      |

| 15.3.4 Operation in Synchronous Mode                                         |      |

| 15.4 SCI Interrupt Sources and DMAC                                          |      |

| 15.5 Usage Notes                                                             | 548  |

| Section 16 Serial Communication Interface with FIFO (SCIF)                   | 553  |

| 16.1 Overview                                                                |      |

| 16.1.1 Features                                                              |      |

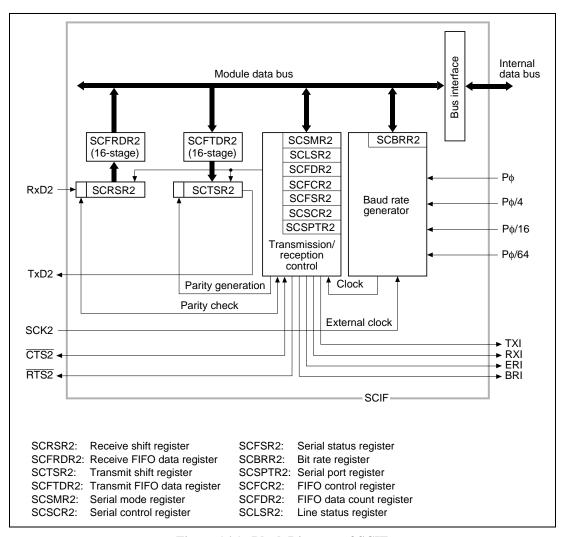

| 16.1.2 Block Diagram.                                                        |      |

| 16.1.3 Pin Configuration.                                                    |      |

| 16.1.4 Degister Configuration                                                |      |

| 16.2 Register Descriptions                   | 558  |

|----------------------------------------------|------|

| 16.2.1 Receive Shift Register (SCRSR2)       | 558  |

| 16.2.2 Receive FIFO Data Register (SCFRDR2)  | 558  |

| 16.2.3 Transmit Shift Register (SCTSR2)      | 559  |

| 16.2.4 Transmit FIFO Data Register (SCFTDR2) | 559  |

| 16.2.5 Serial Mode Register (SCSMR2)         |      |

| 16.2.6 Serial Control Register (SCSCR2)      |      |

| 16.2.7 Serial Status Register (SCFSR2)       | 565  |

| 16.2.8 Bit Rate Register (SCBRR2)            | 572  |

| 16.2.9 FIFO Control Register (SCFCR2)        | 573  |

| 16.2.10 FIFO Data Count Register (SCFDR2)    | 575  |

| 16.2.11 Serial Port Register (SCSPTR2)       |      |

| 16.2.12 Line Status Register (SCLSR2)        | 581  |

| 16.3 Operation                               |      |

| 16.3.1 Overview                              | 582  |

| 16.3.2 Serial Operation                      | 584  |

| 16.4 SCIF Interrupt Sources and the DMAC     | 594  |

| 16.5 Usage Notes                             | 595  |

| Section 17 Smart Card Interface              | 599  |

| 17.1 Overview                                |      |

| 17.1.1 Features                              |      |

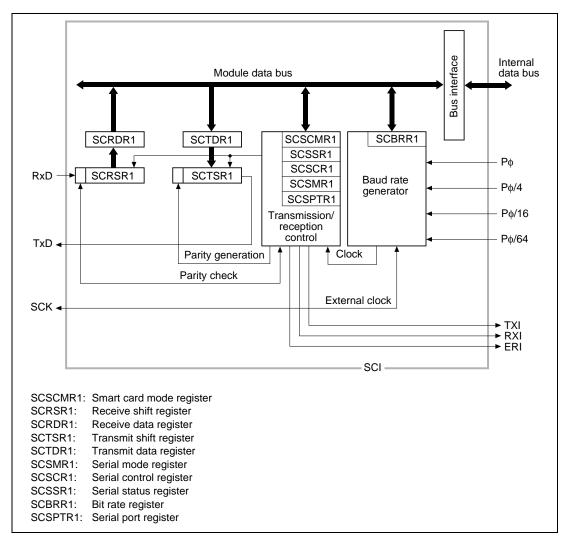

| 17.1.2 Block Diagram                         |      |

| 17.1.3 Pin Configuration                     |      |

| 17.1.4 Register Configuration                |      |

| 17.2 Register Descriptions                   |      |

| 17.2.1 Smart Card Mode Register (SCSCMR1)    |      |

| 17.2.2 Serial Mode Register (SCSMR1)         |      |

| 17.2.3 Serial Control Register (SCSCR1)      |      |

| 17.2.4 Serial Status Register (SCSSR1)       |      |

| 17.3 Operation                               |      |

| 17.3.1 Overview                              |      |

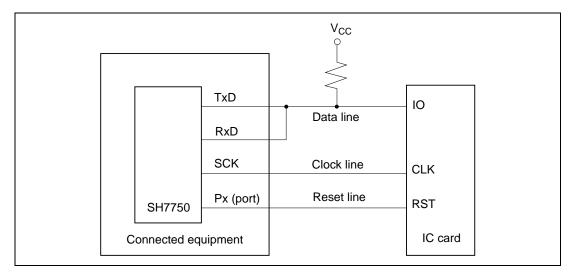

| 17.3.2 Pin Connections                       |      |

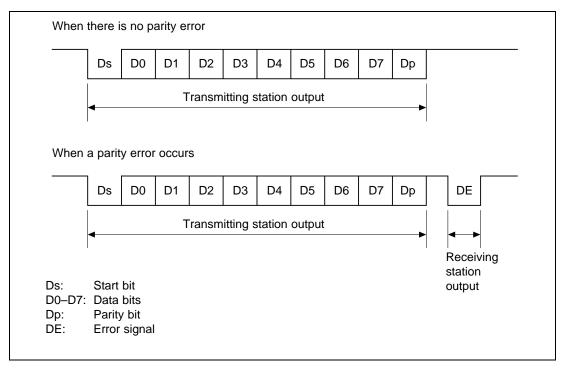

| 17.3.3 Data Format                           |      |

| 17.3.4 Register Settings                     |      |

| 17.3.5 Clock                                 |      |

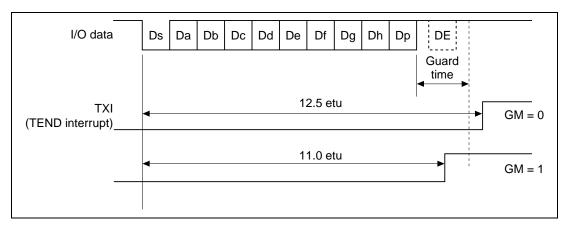

| 17.3.6 Data Transfer Operations              |      |

| 17.4 Usage Notes                             |      |

| Section 18 I/O Ports                         | .629 |

| 18.1 Overview                                |      |

| 18.1.1 Features                              |      |

|                                              | 630  |

Rev. 2.0, 02/99, page ix of xii

| 18.1.3 Pin Configuration                               | . 636 |

|--------------------------------------------------------|-------|

| 18.1.4 Register Configuration                          | . 638 |

| 18.2 Register Descriptions                             | . 639 |

| 18.2.1 Port Control Register A (PCTRA)                 | . 639 |

| 18.2.2 Port Data Register A (PDTRA)                    | . 640 |

| 18.2.3 Port Control Register B (PCTRB)                 | . 641 |

| 18.2.4 Port Data Register B (PDTRB)                    |       |

| 18.2.5 GPIO Interrupt Control Register (GPIOIC)        | 643   |

| 18.2.6 Serial Port Register (SCSPTR1)                  | . 644 |

| 18.2.7 Serial Port Register (SCSPTR2)                  | . 645 |

| 19.1 Overview                                          | . 649 |

| 19.1.1 Features                                        | . 649 |

| 19.1.2 Block Diagram                                   | . 650 |

| 19.1.3 Pin Configuration                               | 651   |

| 19.1.4 Register Configuration                          | . 651 |

| 19.2 Interrupt Sources                                 | 652   |

| 19.2.1 NMI Interrupt                                   | 652   |

| 19.2.2 IRL Interrupts                                  | 653   |

| 19.2.3 On-Chip Peripheral Module Interrupts            | 655   |

| 19.2.4 Interrupt Exception Handling and Priority       | 656   |

| 19.3 Register Descriptions                             | 659   |

| 19.3.1 Interrupt Priority Registers A to C (IPRA–IPRC) | . 659 |

| 19.3.2 Interrupt Control Register (ICR)                | . 660 |

| 19.4 INTC Operation                                    | . 662 |

| 19.4.1 Interrupt Operation Sequence                    | 662   |

| 19.4.2 Multiple Interrupts                             | 664   |

| 19.4.3 Interrupt Masking with MAI Bit                  | . 664 |

| 19.5 Interrupt Response Time                           | 665   |

| 20.1 Overview                                          | . 667 |

| 20.1.1 Features                                        | . 667 |

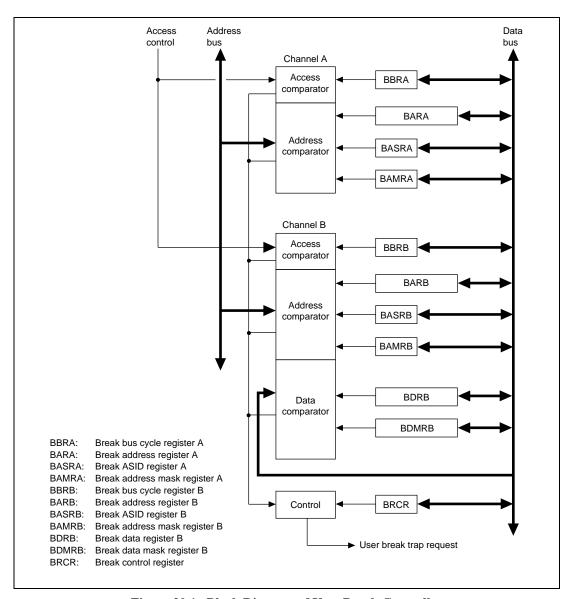

| 20.1.2 Block Diagram                                   | . 668 |

| 20.2 Register Descriptions                             | . 670 |

| 20.2.1 Access to UBC Control Registers                 | . 670 |

| 20.2.2 Break Address Register A (BARA)                 | 671   |

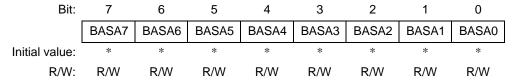

| 20.2.3 Break ASID Register A (BASRA)                   | . 672 |

| 20.2.4 Break Address Mask Register A (BAMRA)           | . 672 |

| 20.2.5 Break Bus Cycle Register A (BBRA)               |       |

| 20.2.6 Break Address Register B (BARB)                 |       |

| 20.2.7 Break ASID Register B (BASRB)                   |       |

| 20.2.8 Break Address Mask Register B (BAMRB)           | . 675 |

| 20.2.9 Break Data Register B (BDRB)                    |       |

| 20.2.10 Break Data Mask Register B (BDMRB)             |       |

| 20.2.11 Break Bus Cycle Register B (BBRB)              | . 677 |

| 20.2.12 Break Control Register (BRCR)                         | 677 |

|---------------------------------------------------------------|-----|

| 20.3 Operation                                                | 680 |

| 20.3.1 Explanation of Terms Relating to Accesses              | 680 |

| 20.3.2 Explanation of Terms Relating to Instruction Intervals | 681 |

| 20.3.3 User Break Operation Sequence                          | 681 |

| 20.3.4 Instruction Access Cycle Break                         | 682 |

| 20.3.5 Operand Access Cycle Break                             | 683 |

| 20.3.6 Condition Match Flag Setting                           |     |

| 20.3.7 Program Counter (PC) Value Saved                       | 684 |

| 20.3.8 Contiguous A and B Settings for Sequential Conditions  |     |

| 20.3.9 Usage Notes                                            |     |

| 20.4 User Break Debug Support Function                        |     |

| 20.5 Examples of Use                                          | 689 |

| •                                                             |     |

| Section 21 Hitachi User Debug Interface (Hitachi-UDI)         | 691 |

| 21.1 Overview                                                 |     |

| 21.1.1 Features                                               | 691 |

| 21.1.2 Block Diagram                                          | 692 |

| 21.1.3 Pin Configuration                                      | 693 |

| 21.1.4 Register Configuration                                 |     |

| 21.2 Register Descriptions                                    |     |

| 21.2.1 Instruction Register (SDIR)                            |     |

| 21.2.2 Data Register (SDDR)                                   | 696 |

| 21.2.3 Bypass Register (SDBPR)                                | 696 |

| 21.3 Operation                                                | 697 |

| 21.3.1 TAP Control                                            | 697 |

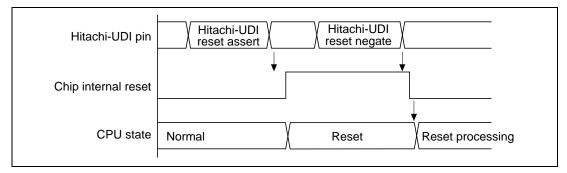

| 21.3.2 Hitachi-UDI Reset                                      | 698 |

| 21.3.3 Hitachi-UDI Interrupt                                  | 698 |

| 21.3.4 Bypass                                                 | 698 |

| 21.4 Usage Notes                                              |     |

|                                                               |     |

| Section 22 Pin Description                                    | 700 |

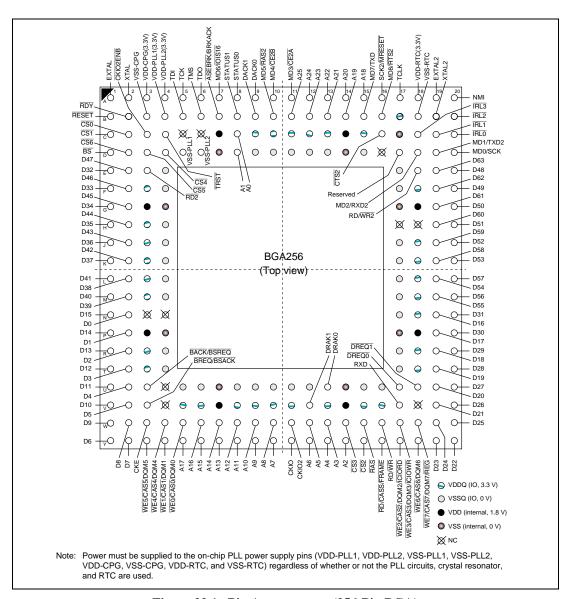

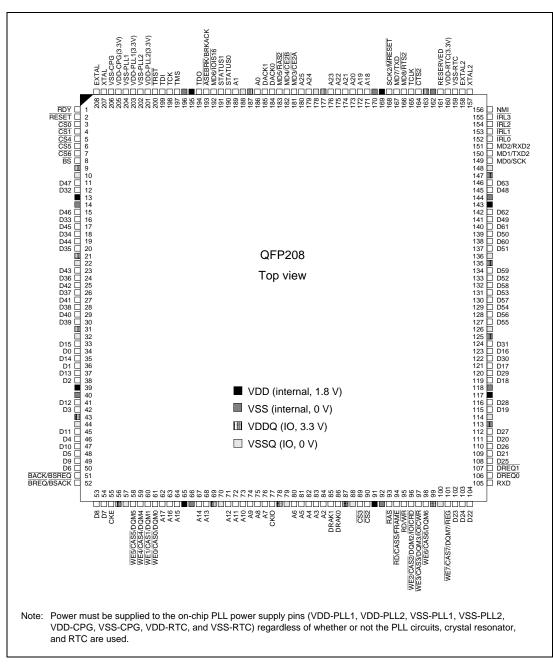

| 22.1 Pin Arrangement                                          | 700 |

| 22.2 Pin Functions                                            | 702 |

| 22.2.1 Pin Functions (256-Pin BGA)                            | 702 |

| 22.2.2 Pin Functions (208-Pin QFP)                            | 712 |

| Section 22 Electrical Characteristics                         | 721 |

| Section 23 Electrical Characteristics                         |     |

| 23.1 Absolute Maximum Ratings                                 |     |

| 23.2 DC Characteristics                                       |     |

| 23.3 AC Characteristics                                       |     |

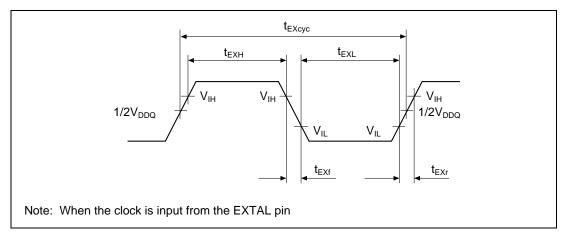

| 23.3.1 Clock and Control Signal Timing                        |     |

| 23.3.2 Control Signal Timing                                  |     |

Rev. 2.0, 02/99, page xi of xii

| 23.3.3. Bus Timing                                      | 734 |

|---------------------------------------------------------|-----|

| 23.3.4 Peripheral Module Signal Timing                  |     |

| 23.3.5 AC Characteristic Test Conditions                |     |

| 23.3.6 Delay Time Variation Due to Load Capacitance     | 789 |

| Appendix A Address List                                 | 791 |

| Appendix B Package Dimensions                           | 795 |

| Appendix C Mode Pin Settings                            | 797 |

| Appendix D CKIO2ENB Pin Configuration                   | 799 |

| Appendix E Pin Functions                                |     |

| E.1 Pin States                                          |     |

| E.2 Handling of Unused Pins                             | 804 |

| Appendix F Synchronous DRAM Address Multiplexing Tables | 805 |

| Appendix G SH7750 On-Demand Data Transfer Mode          | 823 |

| G.1 Pins in DDT Mode                                    |     |

| G.2 Transfer Request Acceptance on Each Channel         |     |

# Section 1 Overview

### **1.1 SH7750** Features

The SH7750 is a 32-bit RISC (reduced instruction set computer) microprocessor, featuring object code upward-compatibility with SH-1, SH-2, SH-3, and SH-3E microcomputers. It includes an 8-kbyte instruction cache, a 16-kbyte operand cache with a choice of copy-back or write-through mode, and an MMU (memory management unit) with a 64-entry fully-associative unified TLB (translation lookaside buffer).

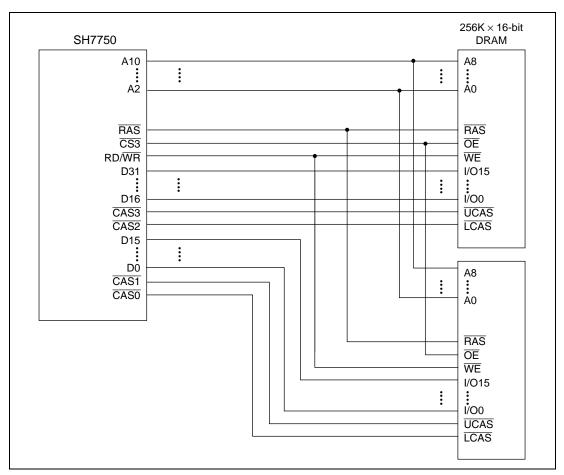

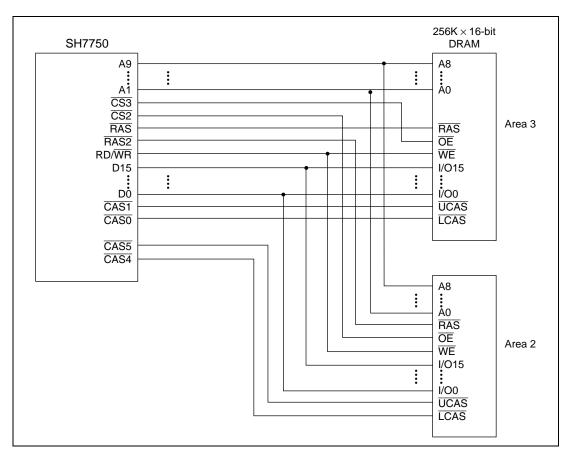

The SH7750 has an on-chip bus state controller (BSC) that allows direct connection to DRAM and synchronous DRAM without external circuitry. Its 16-bit fixed-length instruction set enables program code size to be reduced by almost 50% compared with 32-bit instructions.

The features of the SH7750 are summarized in table 1.1.

Table 1.1 SH7750 Features

| Item | Features                                                                                                              |

|------|-----------------------------------------------------------------------------------------------------------------------|

| LSI  | Operating frequency: 200 MHz                                                                                          |

|      | Performance:                                                                                                          |

|      | — 360 MIPS (200 MHz)                                                                                                  |

|      | — 1.4 GFLOPS (200 MHz)                                                                                                |

|      | Superscalar architecture: Parallel execution of two instructions                                                      |

|      | <ul><li>Voltage: 1.8 V (internal), 3.3 V (I/O)</li></ul>                                                              |

|      | Packages: 256-pin BGA, 208-pin QFP                                                                                    |

|      | External buses                                                                                                        |

|      | <ul> <li>Separate 26-bit address and 64-bit data buses</li> </ul>                                                     |

|      | <ul> <li>External bus frequency of 1/2, 1/3, 1/4, 1/6, or 1/8 times internal bus<br/>frequency</li> </ul>             |

| CPU  | Original Hitachi SH architecture                                                                                      |

|      | 32-bit internal data bus                                                                                              |

|      | General register file:                                                                                                |

|      | <ul> <li>Sixteen 32-bit general registers (and eight 32-bit shadow registers)</li> </ul>                              |

|      | <ul> <li>Seven 32-bit control registers</li> </ul>                                                                    |

|      | Four 32-bit system registers                                                                                          |

|      | RISC-type instruction set (upward-compatible with SH Series)                                                          |

|      | <ul> <li>Fixed 16-bit instruction length for improved code efficiency</li> </ul>                                      |

|      | <ul> <li>Load-store architecture</li> </ul>                                                                           |

|      | <ul> <li>Delayed branch instructions</li> </ul>                                                                       |

|      | <ul> <li>Conditional execution</li> </ul>                                                                             |

|      | <ul> <li>C-based instruction set</li> </ul>                                                                           |

|      | <ul> <li>Superscalar architecture (providing simultaneous execution of two<br/>instructions) including FPU</li> </ul> |

|      | Instruction execution time: Maximum 2 instructions/cycle                                                              |

|      | Virtual address space: 4 Gbytes (448-Mbyte external memory space)                                                     |

|      | Space identifier ASIDs: 8 bits, 256 virtual address spaces                                                            |

|      | On-chip multiplier                                                                                                    |

|      | Five-stage pipeline                                                                                                   |

Table 1.1 SH7750 Features (cont)

## Item Features

FPU

- · On-chip floating-point coprocessor

- Supports single-precision (32 bits) and double-precision (64 bits)

- Supports IEEE754-compliant data types and exceptions

- Two rounding modes: Round to Nearest and Round to Zero

- Handling of denormalized numbers: Truncation to zero or interrupt generation for compliance with IEEE754

- Floating-point registers: 32 bits × 16 words × 2 banks

(single-precision × 16 words or double-precision × 8 words) × 2 banks

- 32-bit CPU-FPU floating-point communication register (FPUL)

- Supports FMAC (multiply-and-accumulate) instruction

- Supports FDIV (divide) and FSQRT (square root) instructions

- Supports FLDI0/FLDI1 (load constant 0/1) instructions

- Instruction execution times

- Latency (FMAC/FADD/FSUB/FMUL): 3 cycles (single-precision), 8 cycles (double-precision)

- Pitch (FMAC/FADD/FSUB/FMUL): 1 cycle (single-precision), 6 cycles (double-precision)

Note: FMAC is supported for single-precision only.

- 3-D graphics instructions (single-precision only):

- 4-dimensional vector conversion and matrix operations (FTRV): 4 cycles (pitch), 7 cycles (latency)

- 4-dimensional vector (FIPR) inner product: 1 cycle (pitch), 4 cycles (latency)

- Five-stage pipeline

Table 1.1 SH7750 Features (cont)

| Item                           | Features                                                                                                  |

|--------------------------------|-----------------------------------------------------------------------------------------------------------|

| Clock pulse<br>generator (CPG) | <ul> <li>Choice of main clock: 1/2, 1, 3, or 6 times EXTAL</li> <li>Clock modes:</li> </ul>               |

|                                | <ul><li>— CPU frequency: 1, 1/2, 1/3, 1/4, 1/6, or 1/8 times main clock:<br/>maximum 200 MHz</li></ul>    |

|                                | <ul><li>— Bus frequency: 1/2, 1/3, 1/4, 1/6, or 1/8 times main clock: maximum<br/>100 MHz</li></ul>       |

|                                | <ul> <li>Peripheral frequency: 1/2, 1/3, 1/4, 1/6, or 1/8 times main clock:<br/>maximum 50 MHz</li> </ul> |

|                                | Power-down modes                                                                                          |

|                                | — Sleep mode                                                                                              |

|                                | <ul> <li>Standby mode</li> </ul>                                                                          |

|                                | <ul> <li>Module standby function</li> </ul>                                                               |

|                                | Single-channel watchdog timer                                                                             |

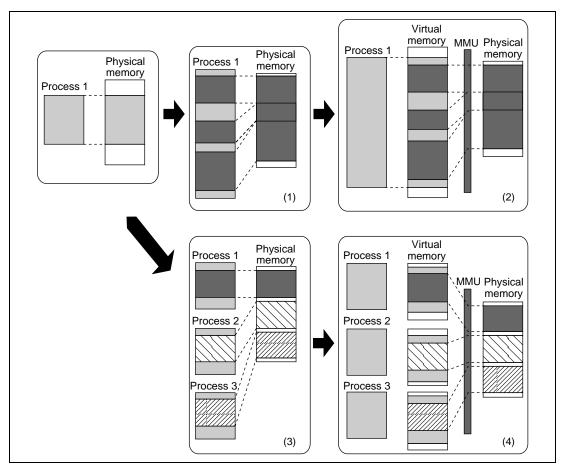

| Memory                         | 4-Gbyte address space, 256 address space identifiers (8-bit ASIDs)                                        |

| management<br>unit (MMU)       | Single virtual mode and multiple virtual memory mode                                                      |

| unit (iviivio)                 | Supports multiple page sizes: 1 kbyte, 4 kbytes, 64 kbytes, 1 Mbyte                                       |

|                                | 4-entry fully-associative TLB for instructions                                                            |

|                                | 64-entry fully-associative TLB for instructions and operands                                              |

|                                | <ul> <li>Supports software-controlled replacement and random-counter replacement algorithm</li> </ul>     |

|                                | TLB contents can be accessed directly by address mapping                                                  |

Table 1.1 SH7750 Features (cont)

| Item                           | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cache memory                   | <ul> <li>Instruction cache (IC) <ul> <li>8 kbytes, direct mapping</li> <li>256 entries, 32-byte block length</li> <li>Normal mode (8-kbyte cache)</li> <li>Index mode</li> </ul> </li> <li>Operand cache (OC) <ul> <li>16 kbytes, direct mapping</li> <li>512 entries, 32-byte block length</li> <li>Normal mode (16-kbyte cache)</li> <li>Index mode</li> <li>RAM mode (8-kbyte cache + 8-kbyte RAM)</li> <li>Choice of write method (copy-back or write-through)</li> </ul> </li> <li>Single-stage copy-back buffer, single-stage write-through buffer</li> <li>Cache memory contents can be accessed directly by address mapping (usable as on-chip memory)</li> <li>Store queue (32 bytes × 2 entries)</li> </ul> |

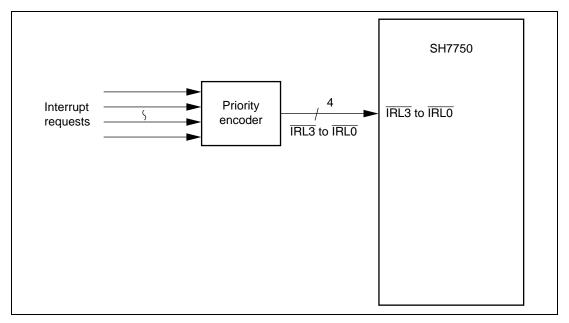

| Interrupt controller (INTC)    | <ul> <li>Five independent external interrupts (NMI, IRL3 to IRL0)</li> <li>15-level signed external interrupts: IRL3 to IRL0</li> <li>On-chip peripheral module interrupts: Priority level can be set for each module</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| User break<br>controller (UBC) | <ul> <li>Supports debugging by means of user break interrupts</li> <li>Two break channels</li> <li>Address, data value, access type, and data size can all be set as break conditions</li> <li>Supports sequential break function</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

Table 1.1 SH7750 Features (cont)

| Item                     | Features                                                                                                           |

|--------------------------|--------------------------------------------------------------------------------------------------------------------|

| Bus state                | Supports external memory access                                                                                    |

| controller (BSC)         | — 64/32/16/8-bit external data bus                                                                                 |

|                          | <ul> <li>External memory space divided into seven areas, each of up to 64</li> </ul>                               |

|                          | Mbytes, with the following parameters settable for each area:                                                      |

|                          | — Bus size (8, 16, 32, or 64 bits)                                                                                 |

|                          | <ul> <li>Number of wait cycles (hardware wait function also supported)</li> </ul>                                  |

|                          | <ul> <li>Direct connection of DRAM, synchronous DRAM, and burst ROM</li> </ul>                                     |

|                          | possible by setting space type                                                                                     |

|                          | <ul> <li>Supports fast page mode and DRAM EDO</li> </ul>                                                           |

|                          | <ul> <li>Supports PCMCIA interface</li> </ul>                                                                      |

|                          | — Chip select signals ( $\overline{\text{CSO}}$ to $\overline{\text{CSO}}$ ) output for relevant areas             |

|                          | <ul> <li>DRAM/synchronous DRAM refresh functions</li> </ul>                                                        |

|                          | <ul> <li>Programmable refresh interval</li> </ul>                                                                  |

|                          | <ul> <li>Supports CAS-before-RAS refresh mode and self-refresh mode</li> </ul>                                     |

|                          | <ul> <li>DRAM/synchronous DRAM burst access function</li> </ul>                                                    |

|                          | Big endian or little endian mode can be set                                                                        |

| Direct memory            | 4-channel physical address DMA controller                                                                          |

| access controller (DMAC) | <ul> <li>Transfer data size: 8, 16, 32, or 64 bits, or 32 bytes</li> </ul>                                         |

| (DIVIAC)                 | Address modes:                                                                                                     |

|                          | <ul> <li>1-bus-cycle single address mode</li> </ul>                                                                |

|                          | <ul> <li>2-bus-cycle dual address mode</li> </ul>                                                                  |

|                          | Transfer requests: External, on-chip module, or auto-requests                                                      |

|                          | Bus modes: Cycle-steal or burst mode                                                                               |

|                          | Supports on-demand data transfer                                                                                   |

| Timer unit (TMU)         | 3-channel auto-reload 32-bit timer                                                                                 |

|                          | Input capture function                                                                                             |

|                          | Choice of seven counter input clocks                                                                               |

| Realtime clock           | On-chip clock and calendar functions                                                                               |

| (RTC)                    | <ul> <li>Built-in 32 kHz crystal oscillator with maximum 1/256 second resolution<br/>(cycle interrupts)</li> </ul> |

Table 1.1 SH7750 Features (cont)

| Item                                                | Features                                                                                                                                                                                                   |

|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Serial<br>communication<br>interface<br>(SCI, SCIF) | <ul> <li>Two full-duplex communication channels (SCI, SCIF)</li> <li>Channel 1 (SCI):  — Choice of asynchronous mode or synchronous mode</li> </ul>                                                        |

|                                                     | <ul> <li>Supports smart card interface</li> <li>Channel 2 (SCIF):         <ul> <li>Supports asynchronous mode</li> <li>Separate 16-byte FIFOs provided for transmitter and receiver</li> </ul> </li> </ul> |

| Packages                                            | • 256-pin BGA, 208-pin QFP                                                                                                                                                                                 |

# 1.2 Block Diagram

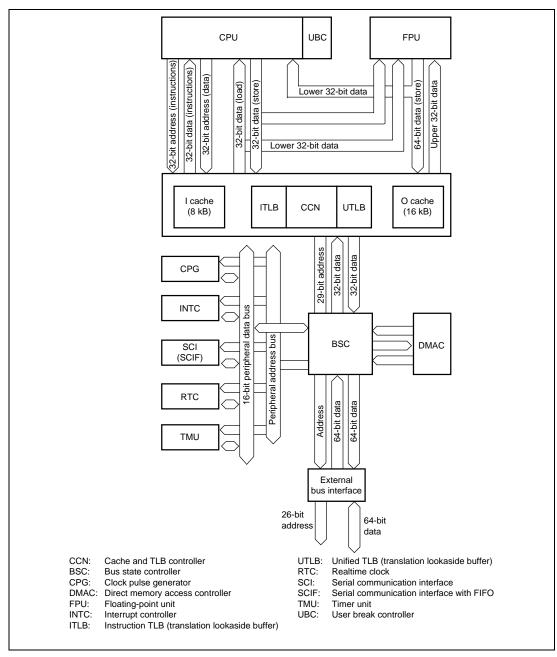

Figure 1.1 shows an internal block diagram of the SH7750.

Figure 1.1 Block Diagram of SH7750 Functions

Rev. 2.0, 02/99, page 8 of 830

# Section 2 Programming Model

# 2.1 Data Formats

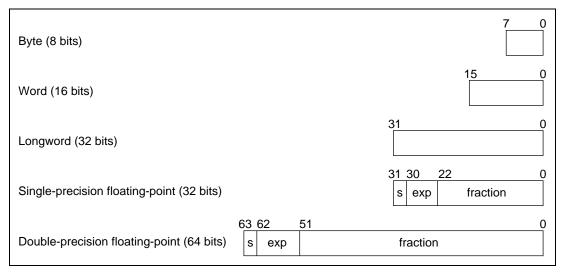

The data formats handled by the SH7750 are shown in figure 2.1.

Figure 2.1 Data Formats

# 2.2 Register Configuration

## 2.2.1 Privileged Mode and Banks

**Processor Modes:** The SH7750 has two processor modes, user mode and privileged mode. The SH7750 normally operates in user mode, and switches to privileged mode when an exception occurs or an interrupt is accepted. There are four kinds of registers—general registers, system registers, control registers, and floating-point registers—and the registers that can be accessed differ in the two processor modes.

**General Registers:** There are 16 general registers, designated R0 to R15. General registers R0 to R7 are banked registers which are switched by a processor mode change.

In privileged mode, the register bank bit (RB) in the status register (SR) defines which banked register set is accessed as general registers, and which set is accessed only through the load control register (LDC) and store control register (STC) instructions.

When the RB bit is 1 (that is, when bank 1 is selected), the 16 registers comprising bank 1 general registers R0\_BANK1 to R7\_BANK1 and non-banked general registers R8 to R15 can be accessed as general registers R0 to R15. In this case, the eight registers comprising bank 0 general registers R0\_BANK0 to R7\_BANK0 are accessed by the LDC/STC instructions. When the RB bit is 0 (that is, when bank 0 is selected), the 16 registers comprising bank 0 general registers R0\_BANK0 to R7\_BANK0 and non-banked general registers R8 to R15 can be accessed as general registers R0 to R15. In this case, the eight registers comprising bank 1 general registers R0\_BANK1 to R7\_BANK1 are accessed by the LDC/STC instructions.

In user mode, the 16 registers comprising bank 0 general registers R0\_BANK0 to R7\_BANK0 and non-banked general registers R8 to R15 can be accessed as general registers R0 to R15. The eight registers comprising bank 1 general registers R0\_BANK1 to R7\_BANK1 cannot be accessed.

Control Registers: Control registers comprise the global base register (GBR) and status register (SR), which can be accessed in both processor modes, and the saved status register (SSR), saved program counter (SPC), vector base register (VBR), saved general register 15 (SGR), and debug base register (DBR), which can only be accessed in privileged mode. Some bits of the status register (such as the RB bit) can only be accessed in privileged mode.

**System Registers:** System registers comprise the multiply-and-accumulate registers (MACH/MACL), the procedure register (PR), the program counter (PC), the floating-point status/control register (FPSCR), and the floating-point communication register (FPUL). Access to these registers does not depend on the processor mode.

Rev. 2.0, 02/99, page 10 of 830

**Floating-Point Registers:** There are thirty-two floating-point registers, FR0–FR15 and XF0–XF15. FR0–FR15 and XF0–XF15 can be assigned to either of two banks (FPR0\_BANK0–FPR15\_BANK0 or FPR0\_BANK1–FPR15\_BANK1).

FR0–FR15 can be used as the eight registers DR0/2/4/6/8/10/12/14 (double-precision floating-point registers, or pair registers) or the four registers FV0/4/8/12 (register vectors), while XF0–XF15 can be used as the eight registers XD0/2/4/6/8/10/12/14 (register pairs) or register matrix XMTRX.

Register values after a reset are shown in table 2.1.

**Table 2.1 Initial Register Values**

| Туре                     | Registers                                          | Initial Value*                                                                                          |

|--------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| General registers        | R0_BANK0-R7_BANK0,<br>R0_BANK1-R7_BANK1,<br>R8-R15 | Undefined                                                                                               |

| Control registers        | SR                                                 | MD bit = 1, RB bit = 1, BL bit = 1, FD bit = 0, I3–I0 = 1111 (H'F), reserved bits = 0, others undefined |

|                          | GBR, SSR, SPC, SGR,<br>DBR                         | Undefined                                                                                               |

|                          | VBR                                                | H'00000000                                                                                              |

| System registers         | MACH, MACL, PR, FPUL                               | Undefined                                                                                               |

|                          | PC                                                 | H'A0000000                                                                                              |

|                          | FPSCR                                              | H'00040001                                                                                              |

| Floating-point registers | FR0-FR15, XF0-XF15                                 | Undefined                                                                                               |

Note: \* Initialized by a power-on reset and manual reset.

The register configuration in each processor is shown in figure 2.2.

Switching between user mode and privileged mode is controlled by the processor mode bit (MD) in the status register.

| 31 0                                                                                                                                                                                          | 31 0                                                                         | 31                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| R0_BANK0*1,*2                                                                                                                                                                                 | R0_BANK1*1,*3                                                                | R0_BANK0*1,*4                                                                          |

| R1_BANK0*2                                                                                                                                                                                    | R1_BANK1*3                                                                   | R1_BANK0*4                                                                             |

| R2_BANK0*2                                                                                                                                                                                    | R2_BANK1*3                                                                   | R2_BANK0*4                                                                             |

| R3_BANK0*2                                                                                                                                                                                    | R3_BANK1*3                                                                   | R3_BANK0*4                                                                             |

| R4_BANK0*2                                                                                                                                                                                    | R4_BANK1*3                                                                   | R4_BANK0*4                                                                             |

| R5_BANK0*2                                                                                                                                                                                    | R5_BANK1*3                                                                   | R5_BANK0*4                                                                             |

| R6_BANK0*2                                                                                                                                                                                    | R6_BANK1*3                                                                   | R6_BANK0*4                                                                             |

| R7_BANK0*2                                                                                                                                                                                    | R7_BANK1*3                                                                   | R7_BANK0*4                                                                             |

| R8                                                                                                                                                                                            | R8                                                                           | R8                                                                                     |

| R9                                                                                                                                                                                            | R9                                                                           | R9                                                                                     |

| R10                                                                                                                                                                                           | R10                                                                          | R10                                                                                    |

| R11                                                                                                                                                                                           | R11                                                                          | R11                                                                                    |

| R12                                                                                                                                                                                           | R12                                                                          | R12                                                                                    |

| R13                                                                                                                                                                                           | R13                                                                          | R13                                                                                    |

| R14                                                                                                                                                                                           | R14                                                                          | R14                                                                                    |

| R15                                                                                                                                                                                           | R15                                                                          | R15                                                                                    |

| N15                                                                                                                                                                                           | N15                                                                          | N15                                                                                    |

| SR                                                                                                                                                                                            | SR                                                                           | SR                                                                                     |

|                                                                                                                                                                                               | SSR                                                                          | SSR                                                                                    |

|                                                                                                                                                                                               |                                                                              |                                                                                        |

| GBR                                                                                                                                                                                           | GBR                                                                          | GBR                                                                                    |

| MACH                                                                                                                                                                                          | MACH                                                                         | MACH                                                                                   |

| MACL                                                                                                                                                                                          | MACL                                                                         | MACL                                                                                   |

| PR                                                                                                                                                                                            | PR                                                                           | PR                                                                                     |

| TIX                                                                                                                                                                                           | VBR                                                                          | VBR                                                                                    |

|                                                                                                                                                                                               | 12.1                                                                         |                                                                                        |

| PC                                                                                                                                                                                            | PC                                                                           | PC                                                                                     |

|                                                                                                                                                                                               | SPC                                                                          | SPC                                                                                    |

|                                                                                                                                                                                               | SGR                                                                          | SGR                                                                                    |

|                                                                                                                                                                                               | DBR                                                                          | DBR                                                                                    |

|                                                                                                                                                                                               | R0_BANK0*1,*4                                                                | R0_BANK1*1,*3                                                                          |

|                                                                                                                                                                                               | R1_BANK0*4                                                                   |                                                                                        |

|                                                                                                                                                                                               | R2_BANK0*4                                                                   | R1_BANK1*3                                                                             |

|                                                                                                                                                                                               |                                                                              | R2_BANK1*3                                                                             |

|                                                                                                                                                                                               | R3_BANK0*4                                                                   | R3_BANK1*3                                                                             |

|                                                                                                                                                                                               | R4_BANK0*4                                                                   | R4_BANK1*3                                                                             |

|                                                                                                                                                                                               | R5_BANK0*4                                                                   | R5_BANK1*3                                                                             |

|                                                                                                                                                                                               | R6_BANK0*4                                                                   | R6_BANK1*3                                                                             |

|                                                                                                                                                                                               | R7_BANK0*4                                                                   | R7_BANK1*3                                                                             |

| (a) Register configuration in user mode                                                                                                                                                       | <ul><li>(b) Register configuration in<br/>privileged mode (RB = 1)</li></ul> | <ul><li>(c) Register configuration in<br/>privileged mode (RB = 0</li></ul>            |

| in user mode  tes: 1. The R0 register is used as indexed GBR indirect addr  2. Banked registers  3. Banked registers  Accessed as general regis LDC/STC instructions whe  4. Banked registers | privileged mode (RB = 1) the index register in indexed register              | privileged mode (RB = 0 r-indirect addressing mode and e SR register. Accessed only by |

Figure 2.2 CPU Register Configuration in Each Processor Mode

Rev. 2.0, 02/99, page 12 of 830

# 2.2.2 General Registers

Figure 2.3 shows the relationship between the processor modes and general registers. The SH7750 has twenty-four 32-bit general registers (R0\_BANK0-R7\_BANK0, R0\_BANK1-R7\_BANK1, and R8-R15). However, only 16 of these can be accessed as general registers R0-R15 in one processor mode. The SH7750 has two processor modes, user mode and privileged mode, in which R0-R7 are assigned as shown below.

# • R0\_BANK0-R7\_BANK0

In user mode (SR.MD = 0), R0–R7 are always assigned to R0\_BANK0–R7\_BANK0. In privileged mode (SR.MD = 1), R0–R7 are assigned to R0\_BANK0–R7\_BANK0 only when SR.RB = 0.

### • R0\_BANK1-R7\_BANK1

In user mode, R0\_BANK1-R7\_BANK1 cannot be accessed.

In privileged mode, R0-R7 are assigned to R0\_BANK1-R7\_BANK1 only when SR.RB = 1.

| SR.MD = 0 or           |          |                        |

|------------------------|----------|------------------------|

| (SR.MD = 1, SR.RB = 0) |          | (SR.MD = 1, SR.RB = 1) |

| R0                     | R0_BANK0 | R0_BANK0               |

| R1                     | R1_BANK0 | R1_BANK0               |

| R2                     | R2_BANK0 | R2_BANK0               |

| R3                     | R3_BANK0 | R3_BANK0               |

| R4                     | R4_BANK0 | R4_BANK0               |

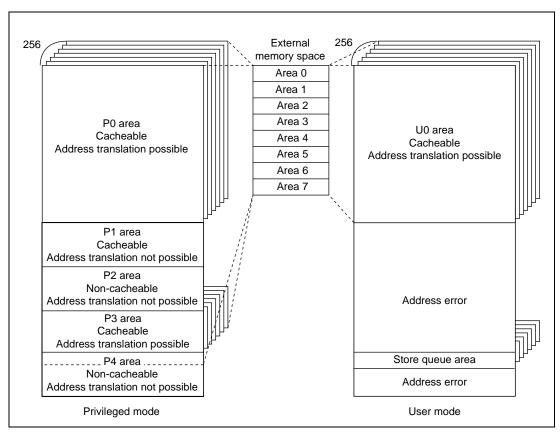

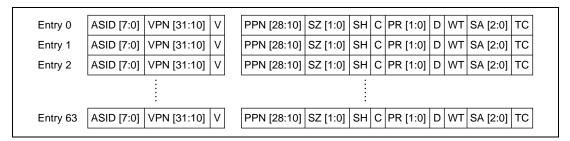

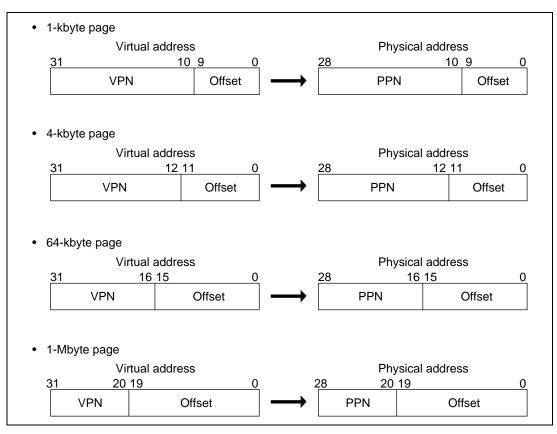

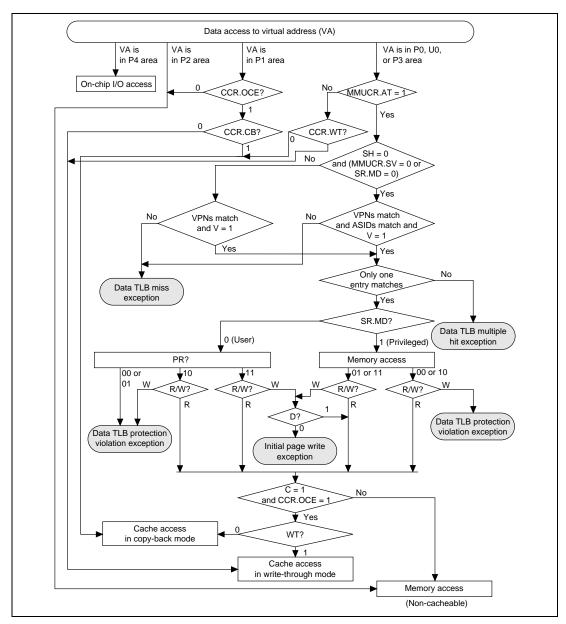

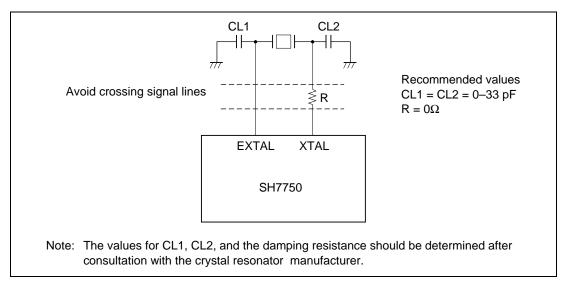

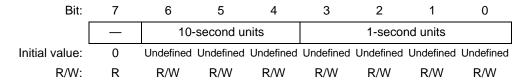

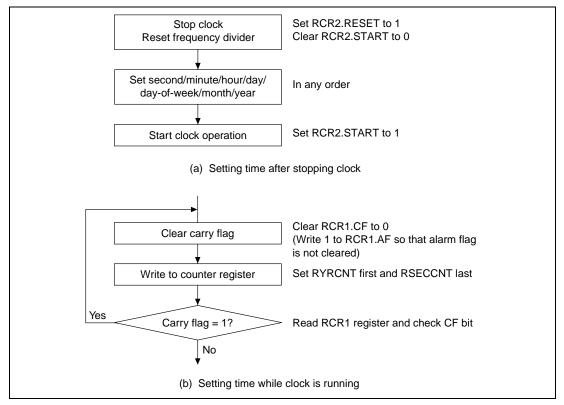

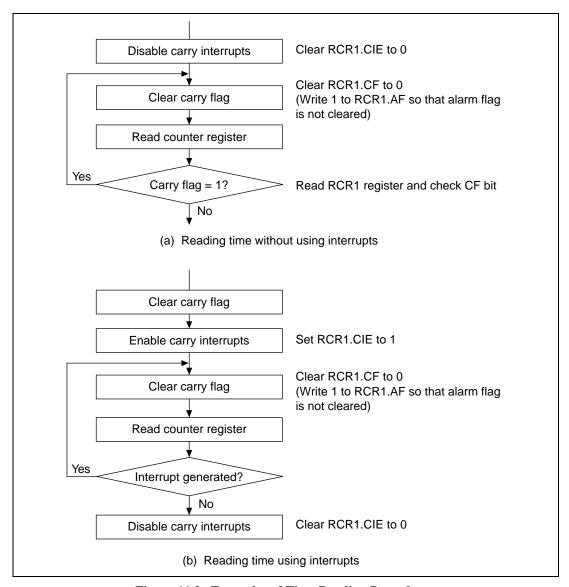

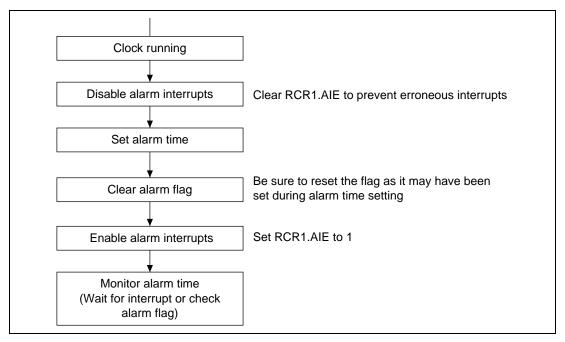

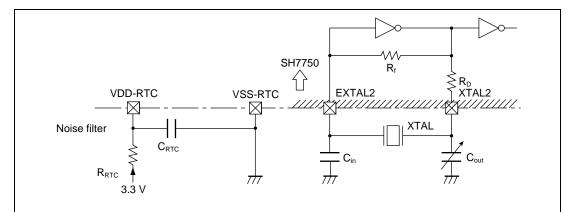

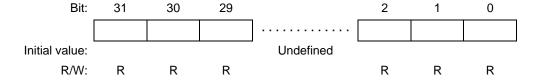

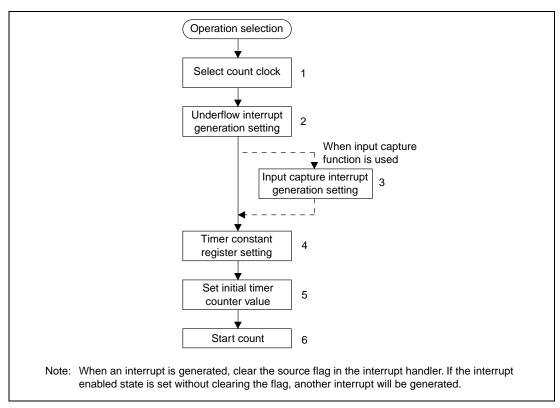

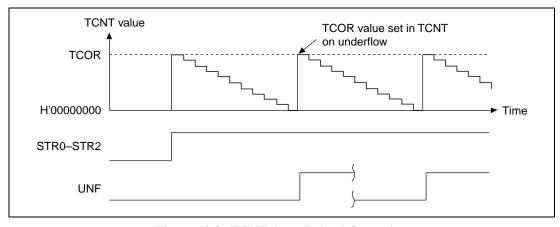

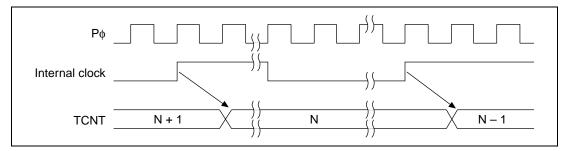

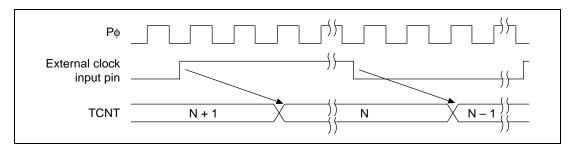

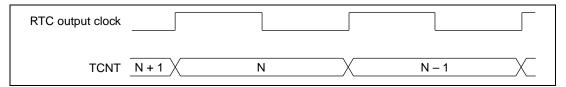

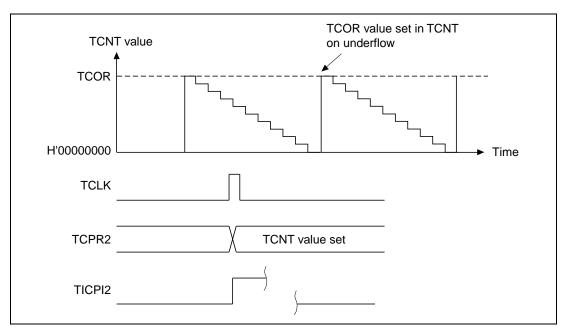

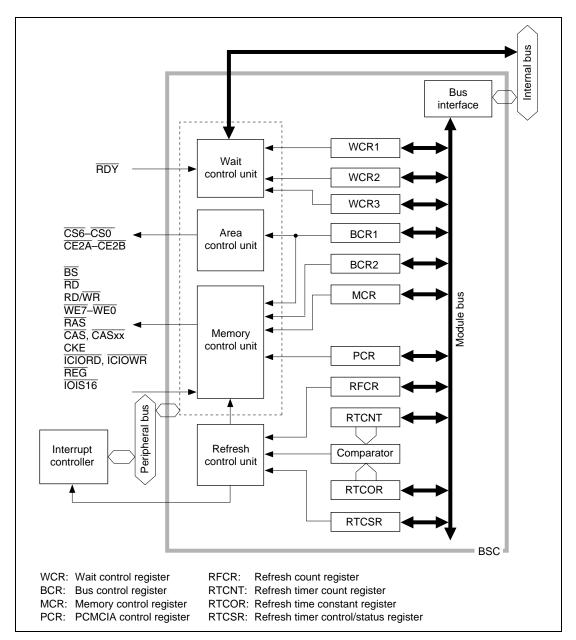

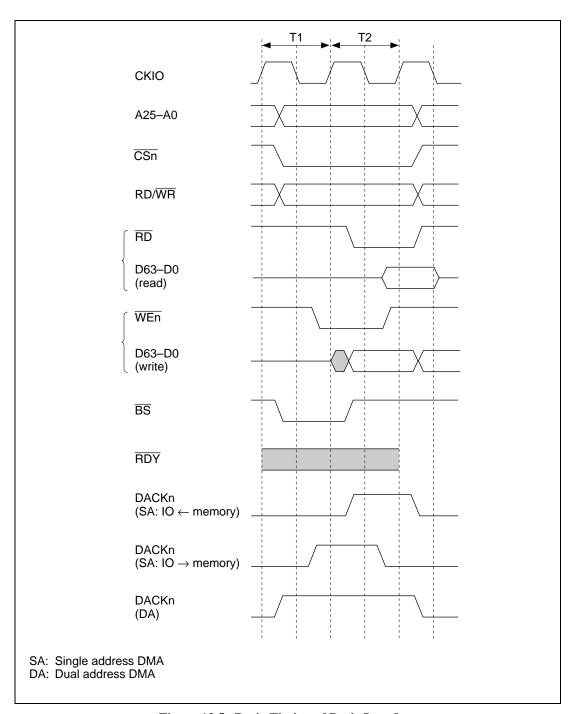

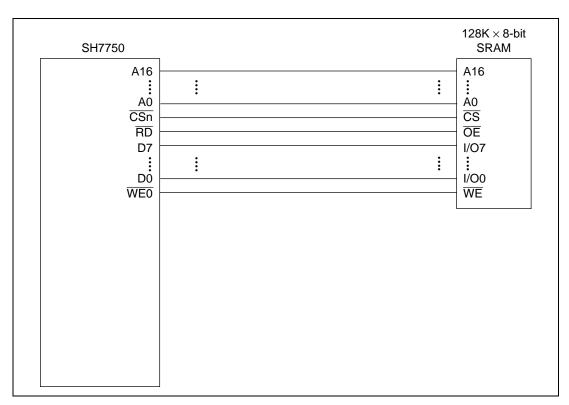

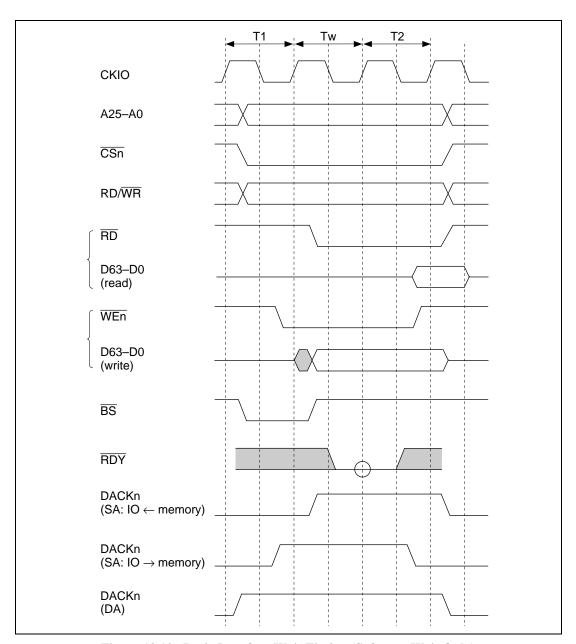

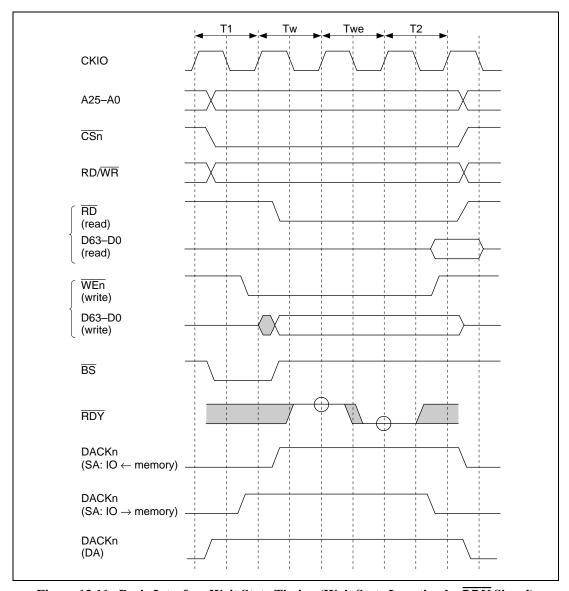

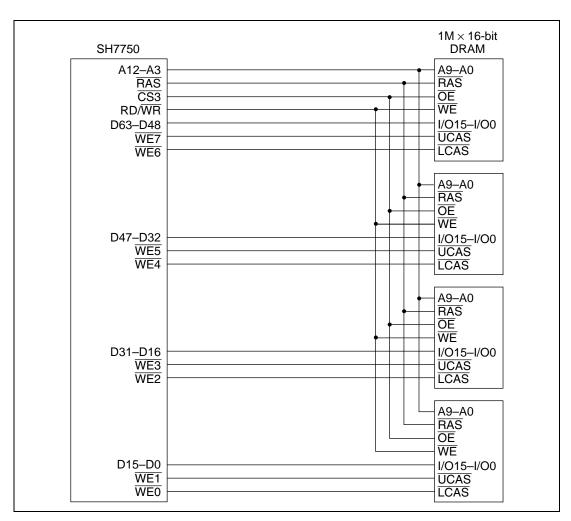

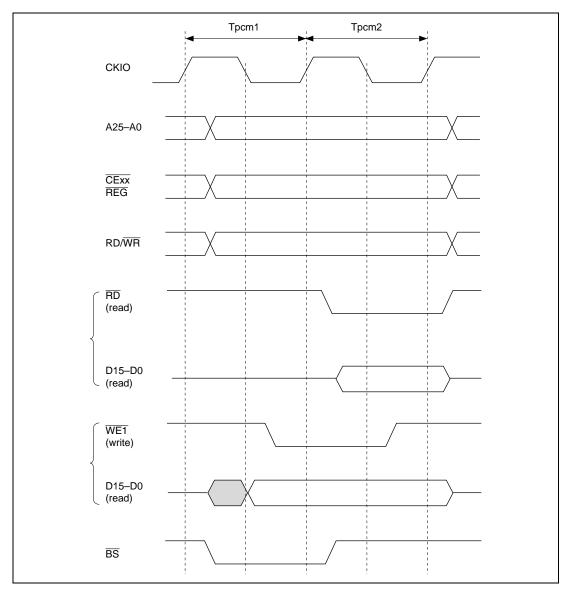

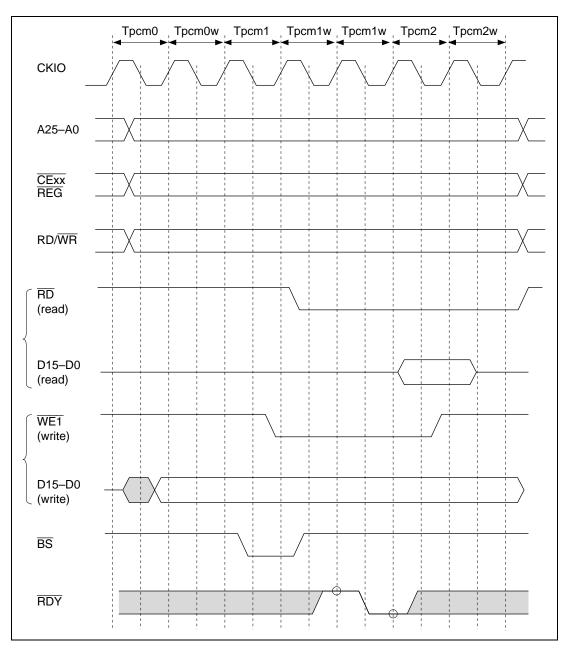

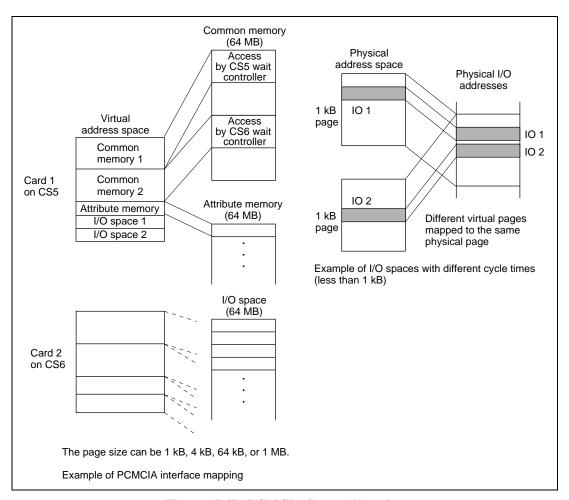

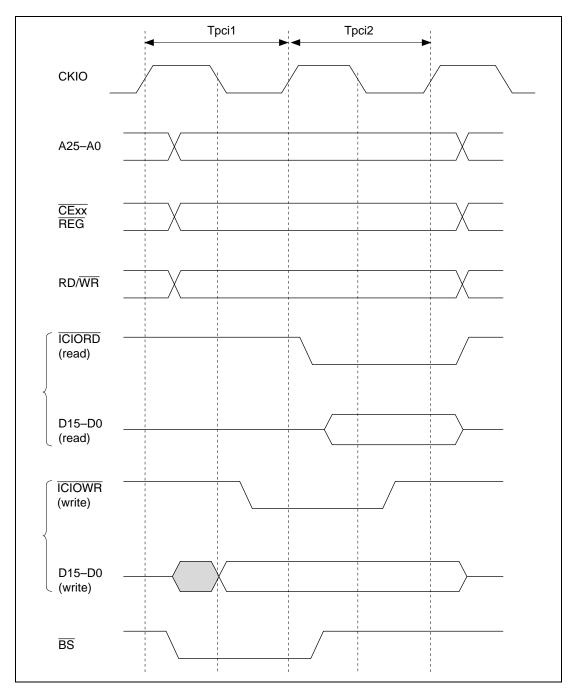

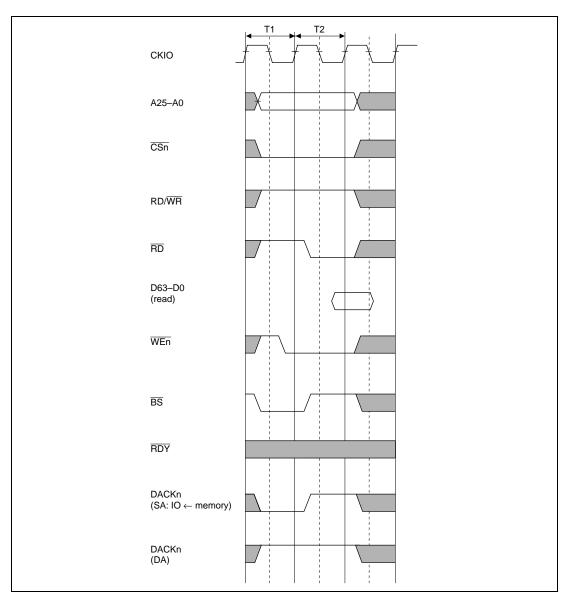

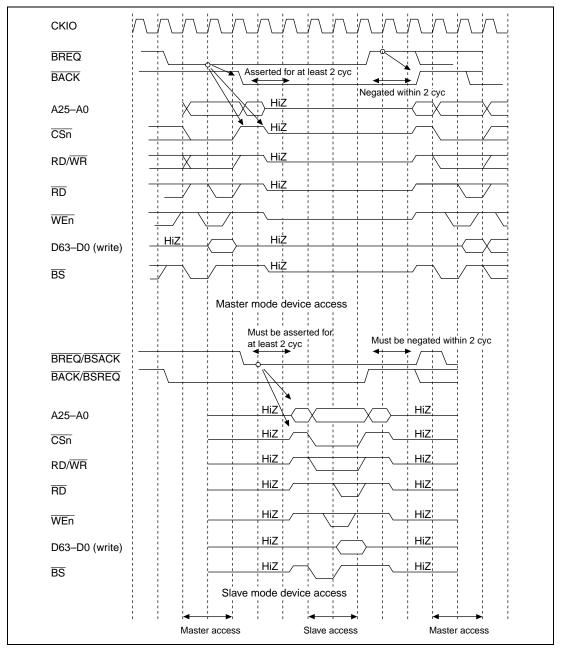

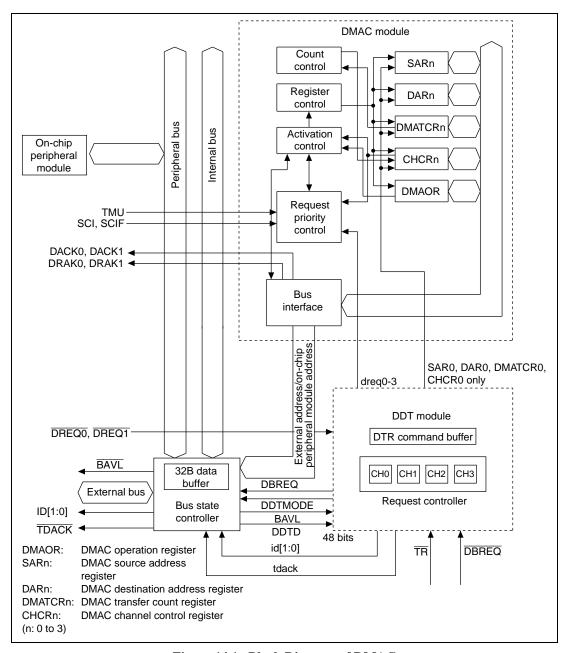

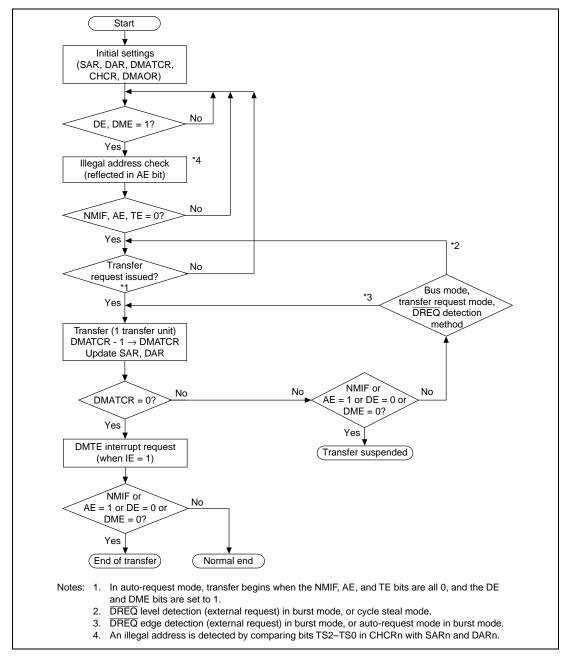

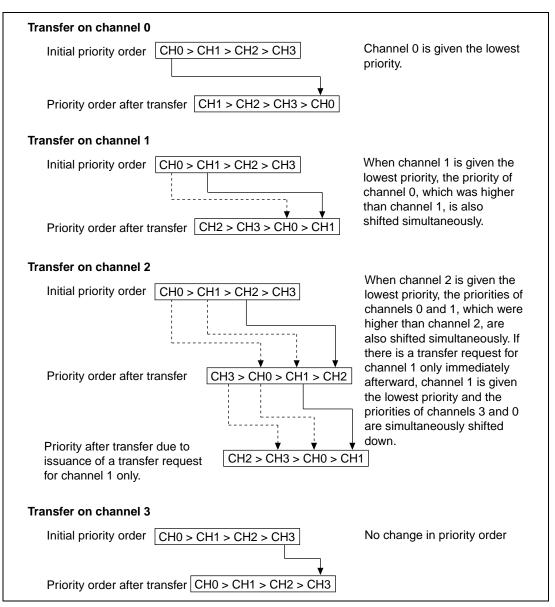

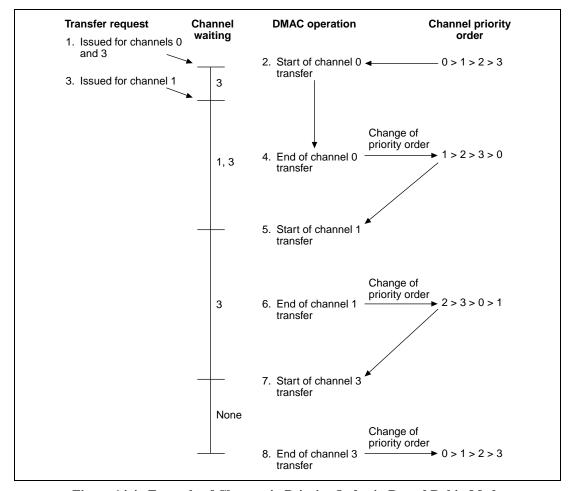

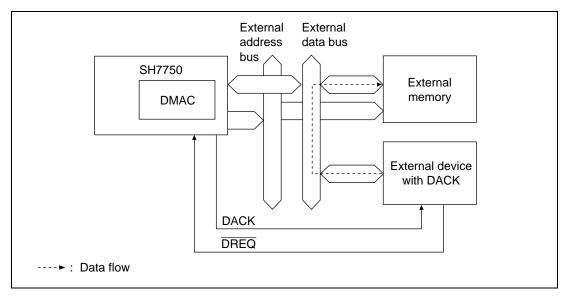

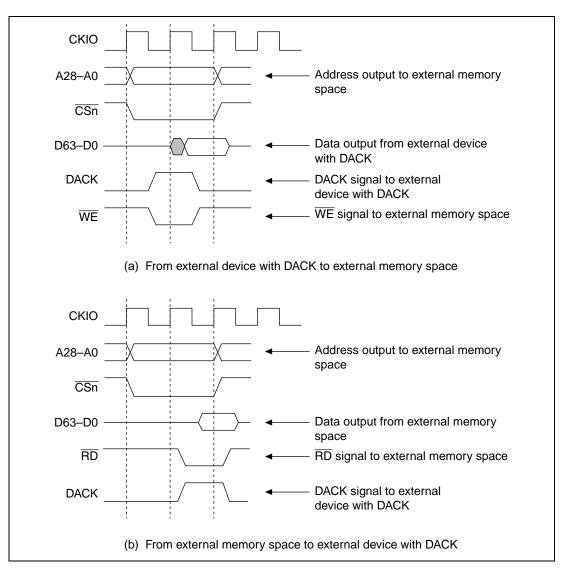

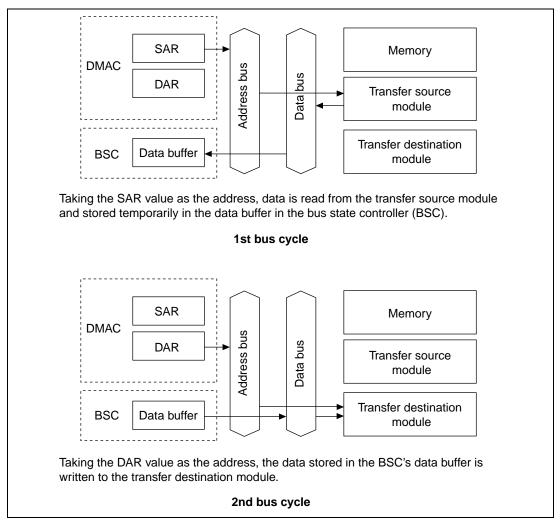

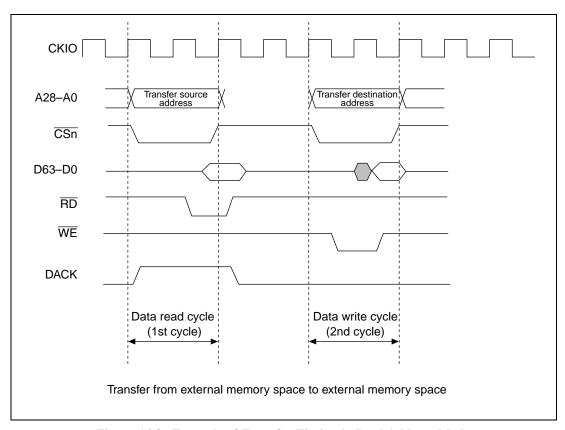

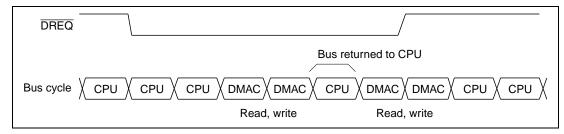

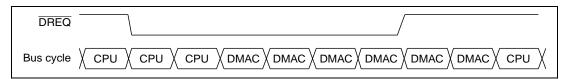

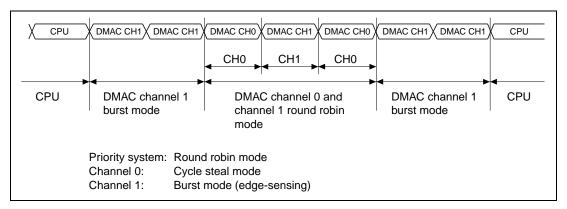

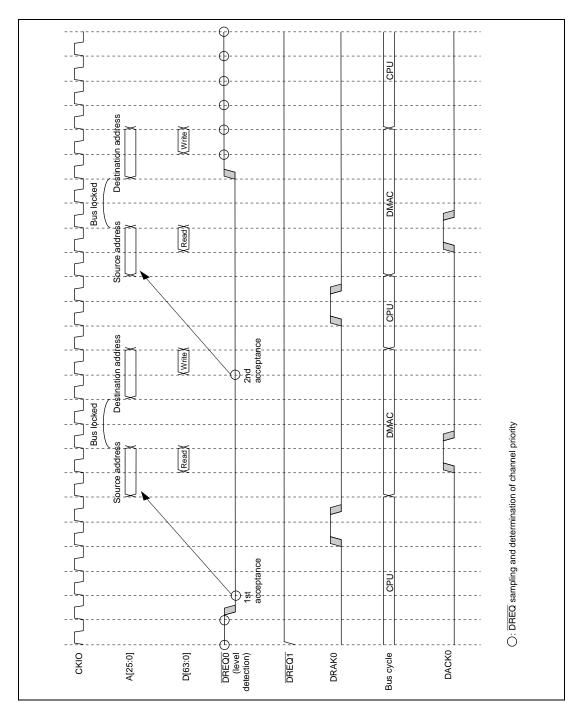

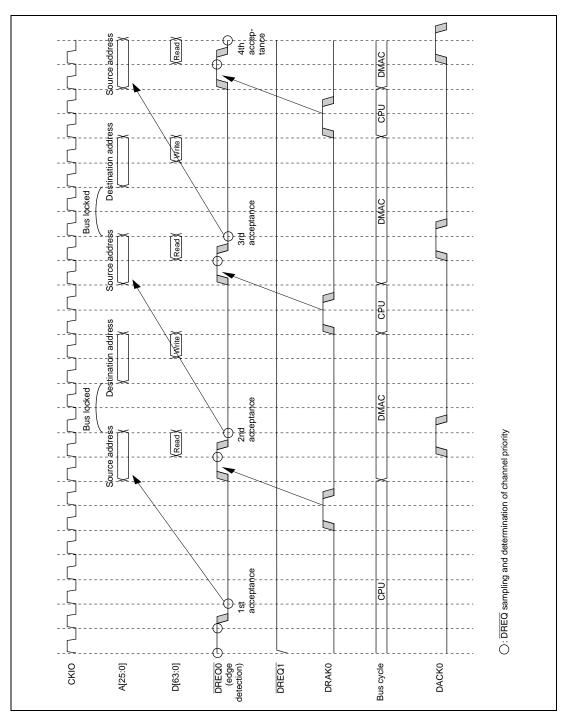

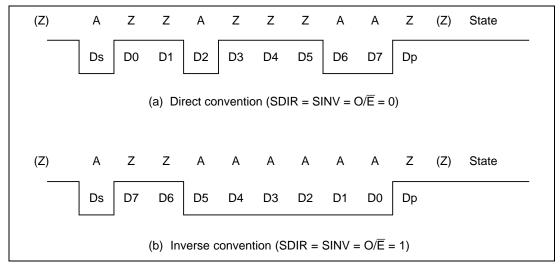

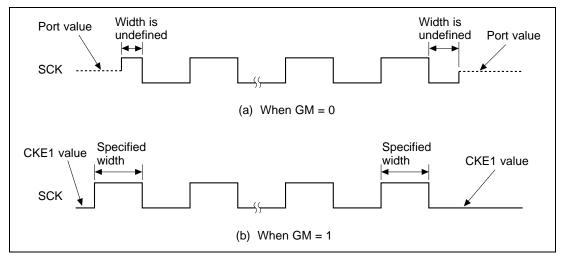

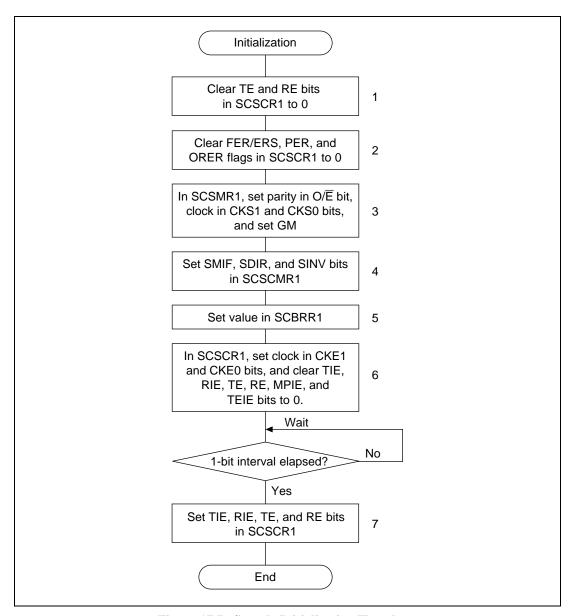

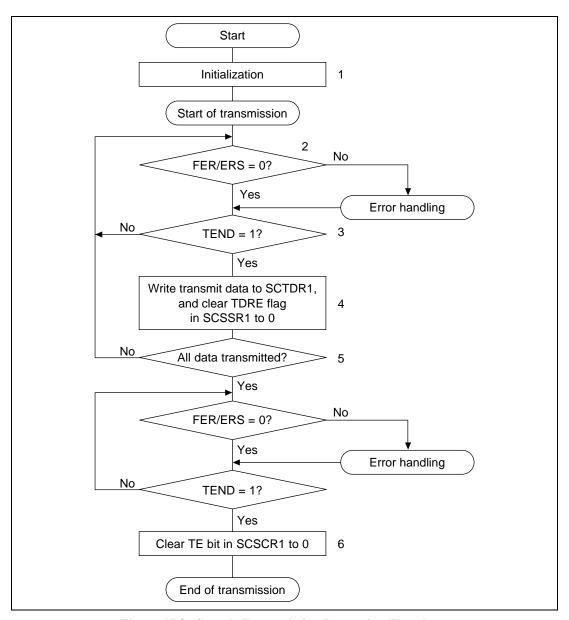

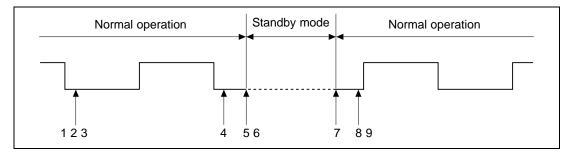

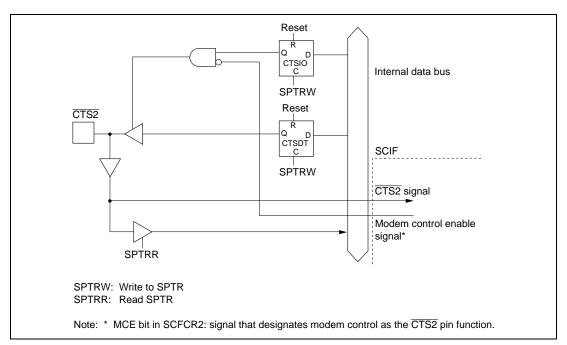

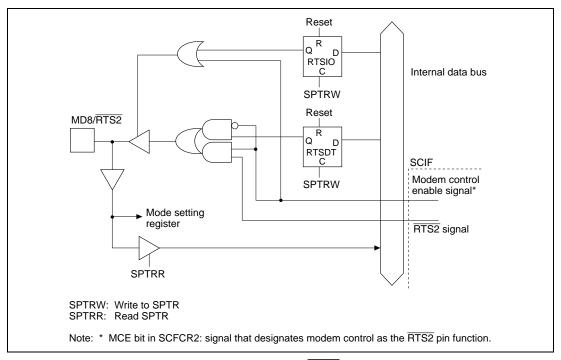

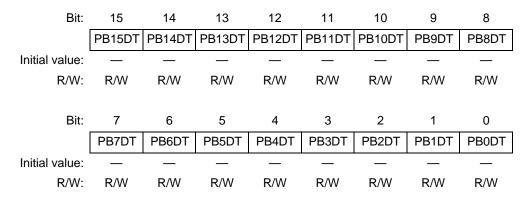

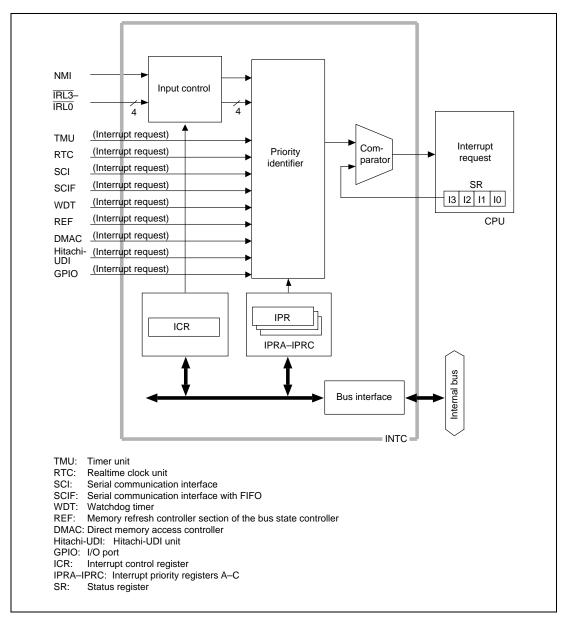

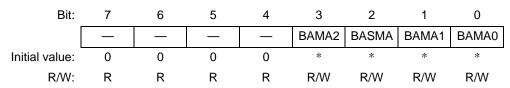

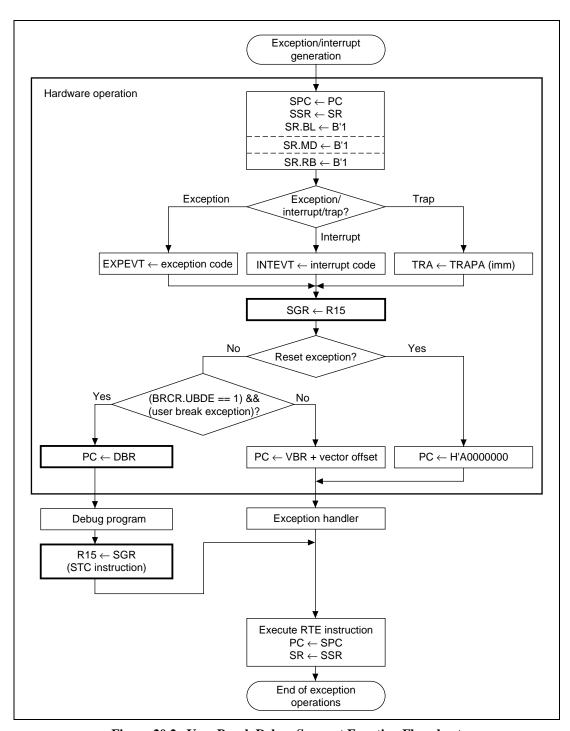

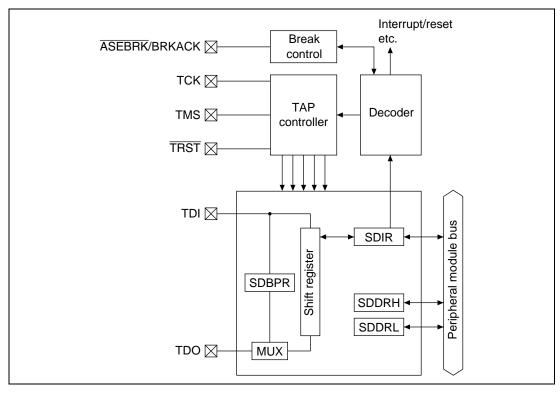

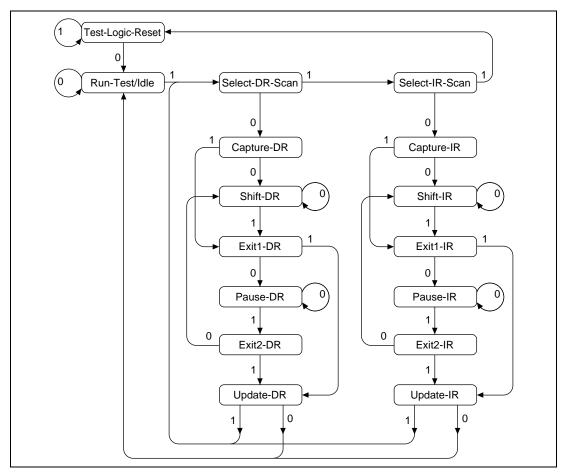

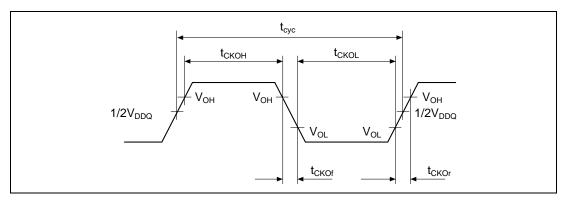

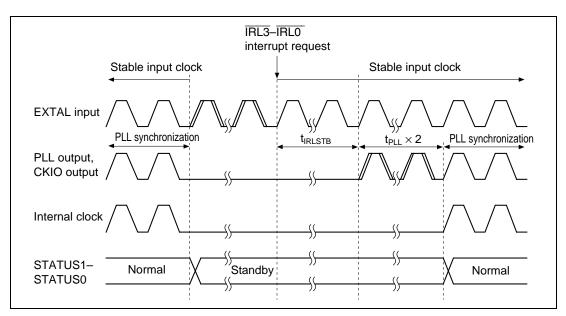

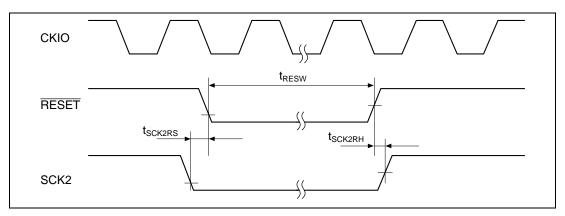

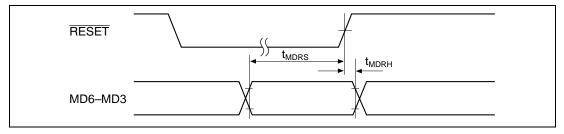

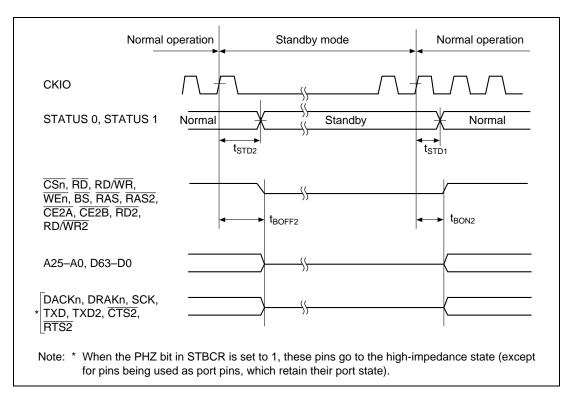

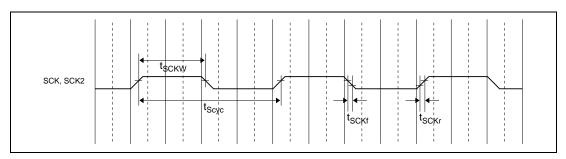

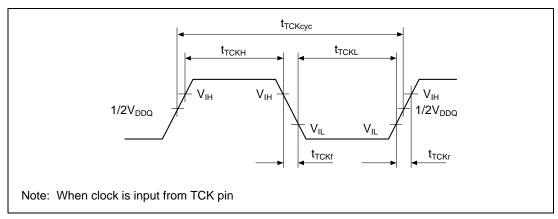

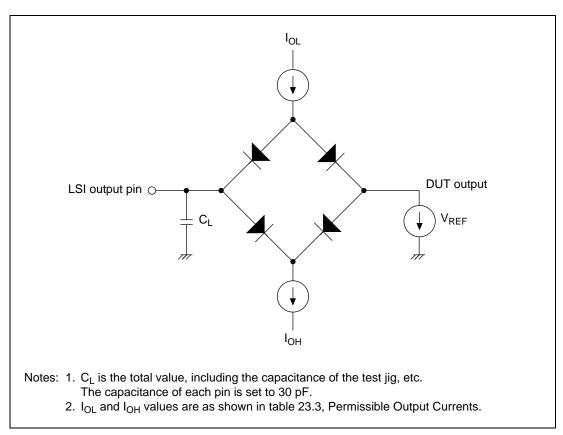

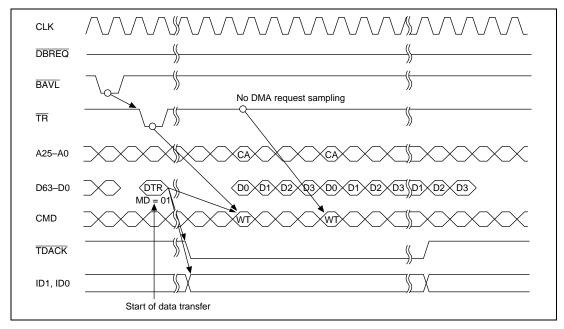

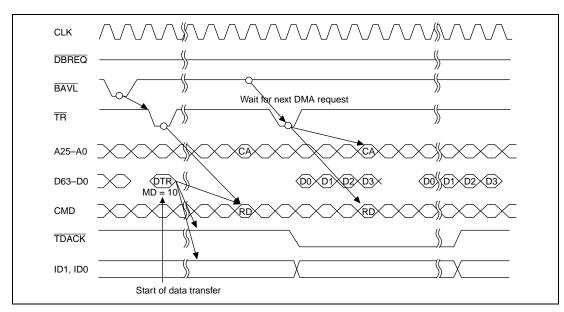

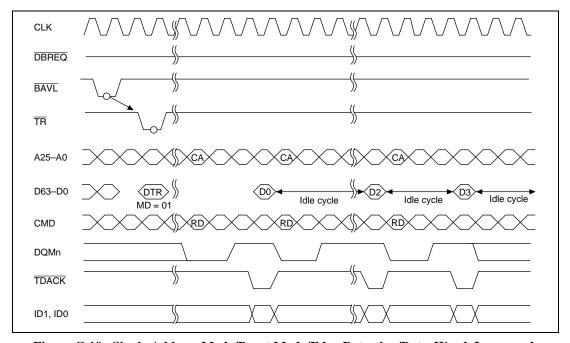

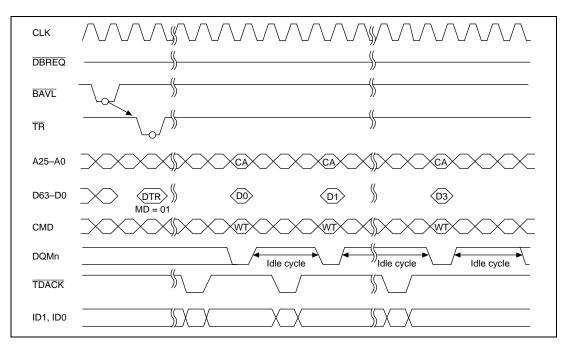

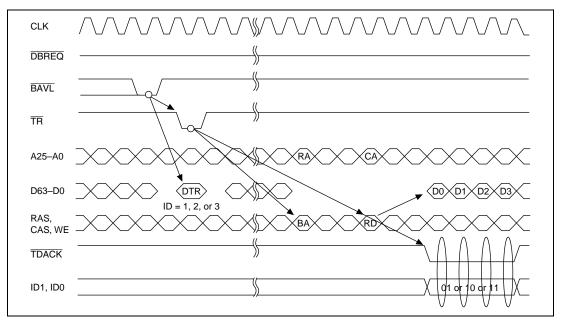

| R5                     | R5_BANK0 | R5_BANK0               |